# MIPI ALLIANCE DEVELOPERS CONFERENCE

Azusena Lupercio Juan Orozco Nestor Hernandez Intel Corporation

I3C<sup>®</sup> Signal Integrity Challenges on DDR5 Based Server Platform Solutions

28-29 SEPTEMBER

#### MIPI.ORG/DEVCON

## Agenda

- Introduction

- DDR5 SPD server connectivity and bus characteristics

- I2C and MIPI I3C Retro-compatibility challenges

- Non-dynamic pullup impact

- Dynamic pullup on open-drain

- Buffer R<sub>ON</sub> design implications

- Critical time margin calculation

- Frequency and AC/DC parameters impact

- Non-monotonic signal behavior

- Slope reversal capability and timing improvement

- Summary

mipi<sup>DEVCON</sup>

MIPI ALLIANCE DEVELOPERS CONFERENCE

#### Introduction

MIPI.ORG/DEVCON

MOBILE & BEYOND

© 2021 MIPI Alliance, Inc.

28-29 SEPTEMBER

## Introduction

2021

- The MIPI I3C Improved Inter-Integrated Circuit interface is first introduced in a server application for the DDR5 DIMM Serial Presence Detect (SPD) function.

- Its implementation exceeds by far the bus capacitance/loading specification, which was defined for low capacitance Mobile/IoT applications.

- This presentation covers the interoperability challenges of the dynamic push-pull and open-drain operating modes on I3C BASIC server applications.

- Covering an in-depth analysis of the implications of long PCB traces, multiple DIMM routing branches, several loads, to the electrical and timing parameters.

MOBILE & BEYOND

#### MIPI.ORG/DEVCON

mipi **DEVCON**

## Introduction cont'd

2021

- I3C Communication Bus specification was released by MIPI Alliance in 2016, as an improved communication protocol compared to its predecessor I2C, but the implementation of I3C, in a Data Center (Server) application was materialized until 2020.

- The main enhancements in I3C adopted by the DDR SPD function are:

- Higher bit rate: up to 12.5MHz, compared to 100KHz-1MHz I2C SPD in prior DDR generations (125x to 12.5x higher bit rate).

- Better IO electrical interface: Push-pull driver vs Open Drain only.

- In-band interrupts (IBI) support Not supported in DDR5 now, but looking for support in the future (or in other Server use cases).

- In band Common Command Codes (CCCs) Direct or Broadcast.

- Reduced interface power (1.0V IOs).

mipi<sup>DEVCON</sup>

## **Introduction cont'd**

2021

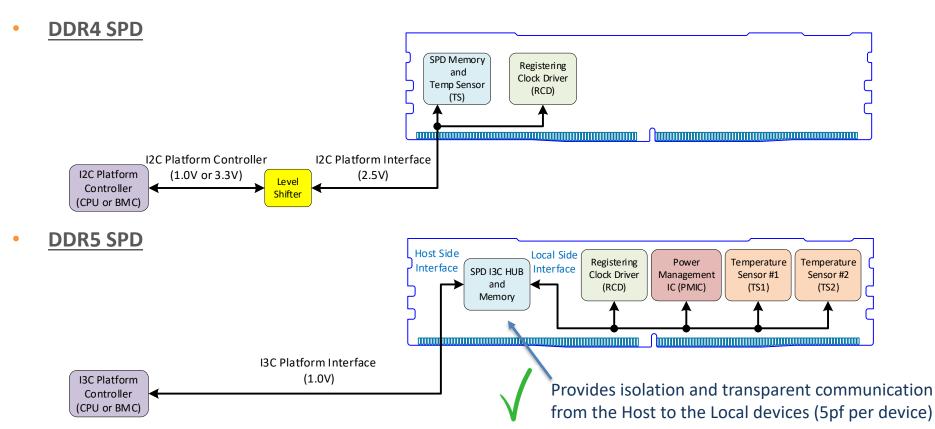

- The DDR5 SPD interface transitioned from I2C to MIPI I3C based on the following requirements for the next generation DDR DIMM technology:

- Lower IO operating Voltage (as low as <u>**1V**</u> aligned to advanced process node)

- DDR4 SPD IO voltage was <u>2.5V</u>

- Higher interface bit rate (400KHz to 8-12.5MHz in real applications) due to the increased number of devices per DIMM to be managed

- DDR4 had <u>two</u> devices per DIMM vs <u>five</u> devices in DDR5

- Considering 8 DIMMs per SPD segment, this is 16 vs 40 devices

- Higher bit rate to reduce boot time (diminishing Memory Reference code execution time)

MOBILE & BEYOND

mipi<sup>DEVCON</sup>

MIPI ALLIANCE DEVELOPERS CONFERENCE

## DDR5 SPD Server connectivity and bus characteristics

28-29 SEPTEMBER

#### MIPI.ORG/DEVCON

## **DDR4 vs DDR5 SPD DIMM Connectivity**

#### MIPI.ORG/DEVCON

2021

#### MOBILE & BEYOND

#### © 2021 MIPI Alliance, Inc. 8

## **DDR4 vs DDR5 SPD DIMM Connectivity**

**DDR4 SPD** SPD Memory Registering and Clock Driver Temp Sensor (RCD) (TS) I2C Platform Controller I2C Platform Interface **I2C Platform** (1.0V or 3.3V) (2.5V) Level Controller Shifter (CPU or BMC) DDR5 SPD Host Side Local Side Registering Interface Interface SPD I3C HUB Clock Driver and (RCD) Memory

> I3C Platform Interface (1.0V)

Host Side Interface Memory Memory Introduces a time delay (12ns round trip) between Host and Local Devices

#### MIPI.ORG/DEVCON

**I3C Platform**

Controller (CPU or BMC)

2021

MIPI ALLIANCE DEVELOPERS CONFERENCE

#### **DDR5 SPD Bus Characteristics**

# 28-29 SEPTEMBER

#### MIPI.ORG/DEVCON

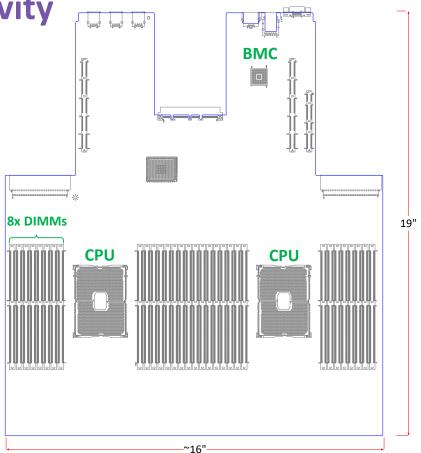

## **DDR5 SPD Platform Connectivity**

- Host side Server PCB routing

- Total length could exceed 50"

2021

- Server motherboards are BIG: up to 16"x 19"

- BMC controller is located at the North side

- DIMMs are located at the South side

- CPU to DIMM SPD routing has lower priority than high speed IO routing (DDR5, PCIe G4/G5, etc.)

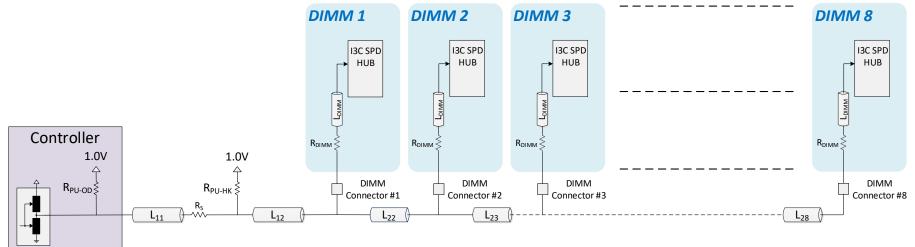

## **Routing length and capacitance**

- Host side Server PCB routing

- From Controller to DIMMs (L<sub>11</sub>+L<sub>12</sub>+L<sub>2x</sub>): ~25"

- DIMM routing (L<sub>DIMM</sub>): 3.5"/DIMM, 28" 8x DIMMs

- Total PCB trace length: ~53"

- Host side Total Capacitance

- Each device apports 5pF

- 1 CPU + 8 HUBs =45pF

- PCB routing is ~3pF/in

- 53" \* 3pF = ~159pF

- Totaling:

- Dev (45pF) + PCB (53pF) = ~204pF

#### MIPI.ORG/DEVCON

2021

MIPI ALLIANCE DEVELOPERS CONFERENCE

#### I2C and MIPI I3C Retro-compatibility Challenges

#### MIPI.ORG/DEVCON

#### M@BILE & BEY@ND

© 2021 MIPI Alliance, Inc.

## I2C and MIPI I3C Retro-compatibility Challenges

- There are three operating modes supported by the I3C protocol:

- I2C mode with Open-Drain(OD) buffer class.

- I3C mode with Open-Drain buffer class.

- I3C mode with Push-Pull(PP) buffer class.

- The OD class requires a pullup to set a stable "Logic-high".

- The pullup is set accordingly with the total capacitance on the bus.

- High capacitance busses requires a "Strong pullup"

- Strong pullup guarantees rise time specification to pass.

- The PP class requires a High-Keeper pullup.

- A "Weak pullup" is required to the target device with low current can pull SDA signal low within a minimum low period.

- Weak pull-up lessens the voltage levels disturbances

MIPI I3C Basic Spec requires Dynamic pull-up control to switch between "strong pull-up" and "weak pull-up" to optimize open-drain and push-pull timing requirements.

#### MIPI.ORG/DEVCON

2021

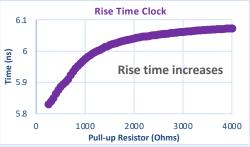

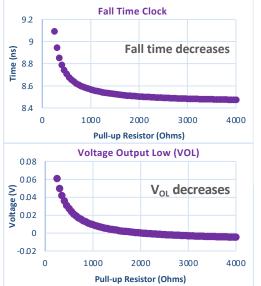

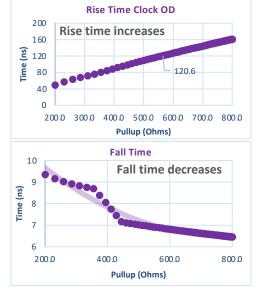

### Non-Dynamic Pullup impact in a 204pF bus

←Push-Pull

#### Open-Drain→

- The Highest the PU

- VIH never reached with pull-up higher than 800 $\Omega$

- Limit max operating frequency

- On-Board PU can guarantee an OD max operating frequency.

- A parallel equivalent  $R_{PU_{-HK}} | | R_{PU_{-OD}}$  of 333.3 $\Omega$

- Rise time=75.3ns

- A pullup ≥ 550Ω negatively affects both rise time and operating frequency

A trade-off among pull-up value, rise time and  $V_{OL}$  is required to meet the highest operating frequency

#### MIPI.ORG/DEVCON

MIPI ALLIANCE DEVELOPERS CONFERENCE

#### **Buffer R**ON design implications

28-29 SEPTEMBER

#### MIPI.ORG/DEVCON

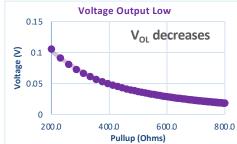

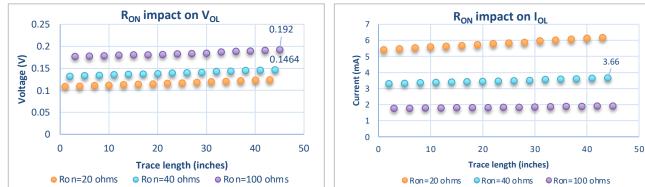

## **Buffer R<sub>ON</sub> value design implications**

- The bigger the R<sub>ON</sub> the higher the V<sub>OL</sub> is:

- Increasing trace length results in higher V<sub>OL</sub>

- With the longest trace length, V<sub>OL</sub>= 192mV,

- Assuming  $V_{IL}$ =0.3V then the transition margin is 108mV

- » Low transition margin can cause idle states

- Setting the  $R_{\text{ON}}$  at 40  $\Omega$  reduces the  $V_{\text{OL}}$

- With the longest trace length V<sub>OL</sub>= 146mV,

- If VIL=0.3V then the transition margin is 154mV

- Notice that at the longest trace length with V<sub>OL</sub>=146mV the I<sub>OL</sub> is 3.66mA

By limiting Ron into a max range of  $40\Omega$  ensures a healthy V<sub>OL</sub> by setting a max I<sub>OL</sub> bigger than 3mA

2021

MIPI ALLIANCE DEVELOPERS CONFERENCE

#### **Critical time margin calculation**

28-29 SEPTEMBER

#### MIPI.ORG/DEVCON

## **Critical time margin calculation**

2021

MIPI.ORG/DEVCON

MOBILE & BEYOND

0.00

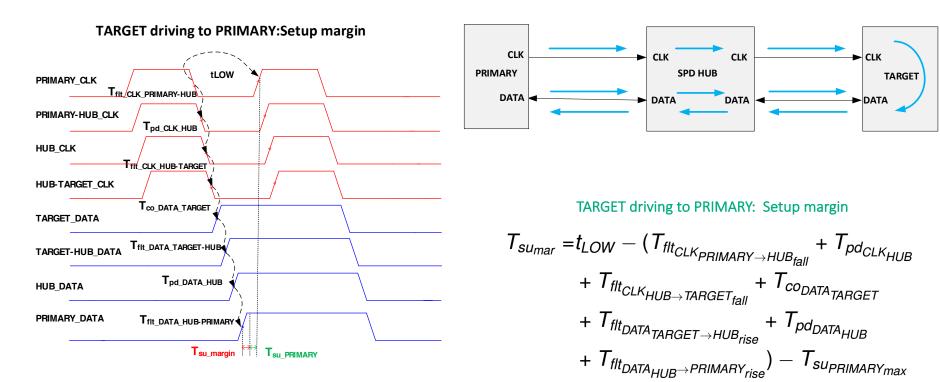

## **Critical time margin calculation**

2021

| Frequency                  | 10          | MHz |

|----------------------------|-------------|-----|

| Duty cycle                 | 35          | %   |

| tLOW                       | <u>65</u>   | ns  |

| tflt_CLK_PRIMARY-HUB_fall  | <u>19.1</u> | ns  |

| tpd_CLK_HUB                | <u>6</u>    | ns  |

| tflt_CLK_HUB-TARGET_fall   | 4.7         | ns  |

| tco_DATA_TARGET            | 12          | ns  |

| tflt_DATA_TARGET-HUB_rise  | 1.972       | ns  |

| tpd_DATA_HUB               | <u>6</u>    | ns  |

| tflt_DATA_HUB-PRIMARY_rise | 9.8         | ns  |

| tsu_PRIMARY_max            | 3           | ns  |

| Setup Margin               | 2.253       | ns  |

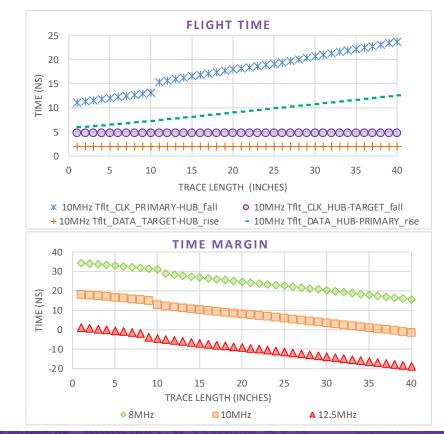

- The longer trace length the biggest flight time

- Inner device propagation delay plays a significant role in defining the operating frequency.

- The highest the Tpd the bigger the time margin reduction.

MOBILE & BEYOND

Increasing tLOW provides extra timing margin.

MIPI.ORG/DEVCON

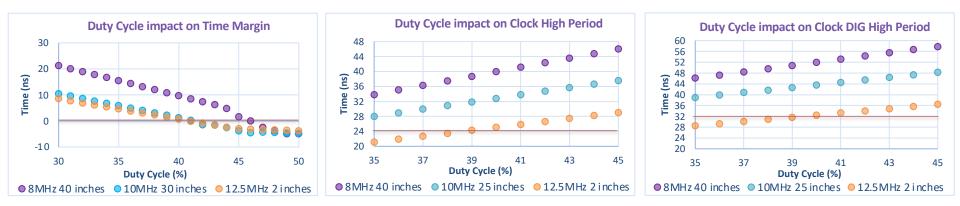

## **Frequency and AC/DC parameters impact**

- Increasing duty cycle reduces tLOW, thus reducing the Time Margin.

- When reducing the Duty Cycle the tHIGH and tDIG\_HIGH are affected.

- Small Duty Cycle can produce a NOT PASS on tHIGH/tDIG\_HIGH.

A correct selection of Duty Cycle provides extra time margin to complete the setup transaction, granting higher operating frequency.

From MIPI I3C Spec  $t_{HIGH}$  min 24ns,  $t_{DIG HIGH}$  min 32ns

2021

## mipi<sup>®</sup> DEVCON

MIPI ALLIANCE DEVELOPERS CONFERENCE

#### Non-monotonic signal behavior

#### MIPI.ORG/DEVCON

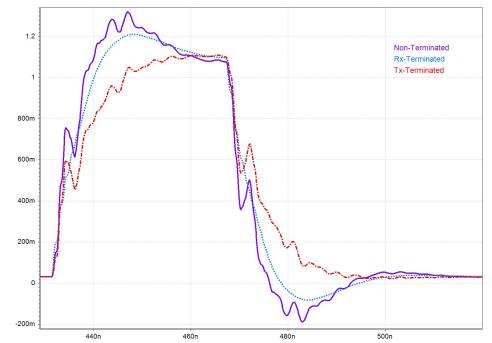

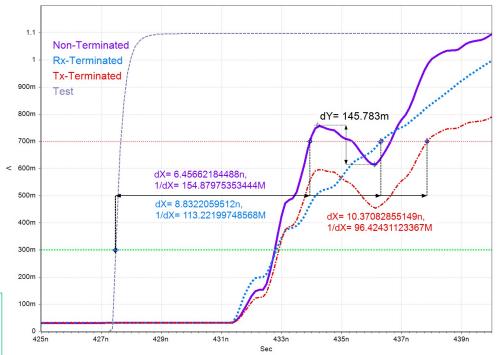

## **Non-monotonic signal behavior**

- Termination effect on transmission lines

- Non-terminated circuit:

2021

- Signal bounces back and forth between the driver and the receiver.

- Tx-terminated circuit:

- Reduces drive strength

- Increases propagation delay

- Limits buffer capabilities

- Rx-terminated circuit:

- Reduces bouncing effect

- Increases propagation delay

MIPI ALLIANCE DEVELOPERS CONFERENCE

## Slope reversal capability and timing improvement

28-29 SEPTEMBER

#### MIPI.ORG/DEVCON

## Slope reversal capability and timing improvement

- With the non-deterministic loading of an unterminated bus, there can be reflections on the bus causing slope reversal on the Rx signal.

- By sampling at the first threshold is possible to filter Non-Monotonicity's; Schmidt triggered inputs

- Non-terminated VS Rx-Terminated:

Improves 2.3ns

- Non-terminated VS Tx-Terminated:

Improves 3.92ns

Slope reversal capability provides additional time margin that improves operating frequency and prevent false logic states.

#### MIPI.ORG/DEVCON

2021

## mipi<sup>®</sup> DEVCON

MIPI ALLIANCE DEVELOPERS CONFERENCE

#### Summary

MIPI.ORG/DEVCON

M@BILE & BEY@ND

© 2021 MIPI Alliance, Inc.

28-29 SEPTEMBER

## Summary

2021

- I3C Applications in Server systems (such as DDR5 SPD) are dealing with higher Bus capacitance than the max limit assumptions in MIPI spec (for 12.5MHz capable buses).

- Higher Bus capacitance applications can be mitigated by using good Buffer Drive strength, strong open-drain class pull-up, and HUB isolation circuits.

- A dynamic pullup operation allows to drive the interoperability challenges between the open-drain and push-pull operating modes; by enabling higher operating frequencies on both modes and limiting critical parameters to meet latest specification.

- Strong buffers tend to increase signal energy reflections, specially in complex topologies resulting with slope reversal conditions at Devices' Inputs.

- Schmitt trigger capable inputs are required in order to mitigate slope reversal conditions when dealing with high bus capacitance and strong buffers

mipi<sup>DEVCON</sup>

## mipi<sup>®</sup> DEVCON

MIPI.ORG/DEVCON

MIPI ALLIANCE DEVELOPERS CONFERENCE

## THANK YOU!

MOBILE & BEYOND

© 2021 MIPI Alliance, Inc.

28-29

SEPTEMBER