Ashraf Takla Mixel, Inc.

MIPI D-PHY<sup>SM</sup> and MIPI CSI-2<sup>SM</sup> for IoT: Al Edge Devices

## **Agenda**

- Benefits of Edge Processing

- Perceive Ergo® Edge Inference Processor Overview

- Block diagram

- target solutions

- Target Applications

- Why MIPI?

- Why FDSOI?

- Mixel MIPI IP and Silicon Results

## **Benefits of Processing at the Edge**

- Latency: able to make decisions in real-time or near real-time vs. increased latency when processing at a data center or in the cloud

- Power savings: smarter devices require less bandwidth, provide less false notifications which can improve battery life

- Security and privacy: reduced chance for breach by reducing transmission of raw data to be processed somewhere else

- Connectivity: in some cases, connecting to broadband or even mobile may not be feasible so local computing is required

- Connection costs: even if connection is available, it may be worthwhile to save bandwidth due to connectivity costs

## Perceive ERGO™

- Edge inference processor for use in devices such as security cameras or smart appliances

- 20-100x more power-efficient, delivering

4 sustained GPU-equivalent floatingpoint TOPS at 55 TOPS/W

- Able to process large neural networks in 20mW and supports a variety of advanced neural networks

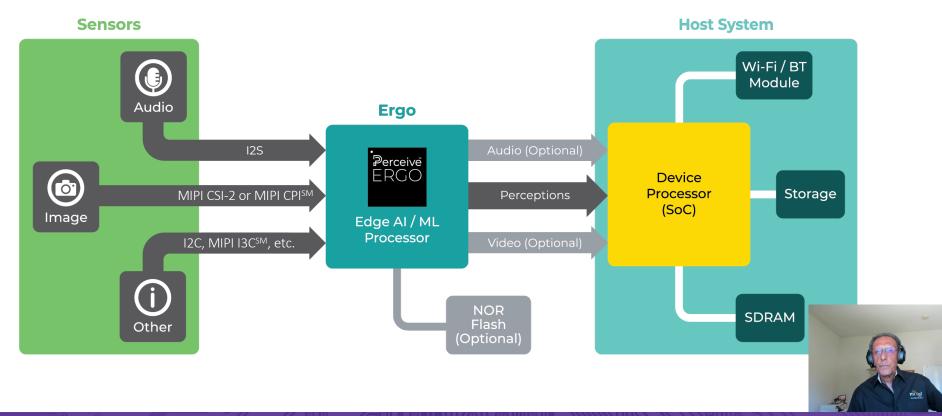

## **Overview of System Design**

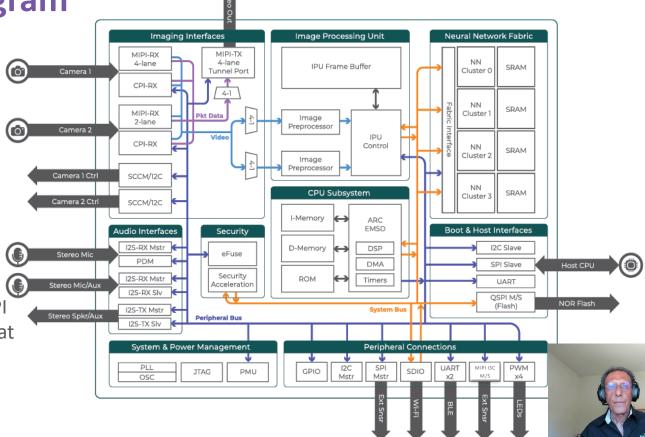

**Ergo Block Diagram**

Built on GLOBALFOUNDRIES® 22FDX® Platform

Integrates Mixel's MIPI D-PHY CSI-2 TX/RX IP at 1.5Gbps/lane

#### **Perceive Target Solutions**

- Video Object Detection

- Enables home or enterprise security to detect interesting motion and ignore false alerts

- **Audio Event Detection**

- Able to detect critical sounds around the device to improve safety and contextual awareness

- Face Recognition

- Can be used as standalone biometric or part of multi-factor authentication to unlock devices or objects

- Speech Recognition

- Used for wakeup words, device-specific commands, and natural language interfaces for smartphone, smart toy, or home appliance

- Smart Home Security Cameras and Doorbells

- Detect interesting motion and ignore false alerts

- Recognize faces, voices, and people

- Detect relevant objects animals, packages, vehicles, etc.

- Use voice for local commands

- Detect important sounds alarms, people, glass breaking, etc.

- Describe people, vehicles, or even the actions in a scene

- Wearables

- Detect important sounds around the user

- Use local voice commands and advanced wake words to simplify device UI

- Recognize faces, people, voice, and emotions

- Detect relevant objects around the user

- Integrate data across multiple sensors

- Portable computing

- Detect and recognize people and faces

- Detect other relevant objects and sounds

- Recognize voices and local voice commands

- Track emotions, attention, and eye location

- Blur or replace video conference backgrounds

- Improve audio or video signal

- Video conferencing

- Detect and track people, faces, and voices

- Recognize individual faces and voices

- Audio noise reduction and intelligent muting

- Use gesture or voice for touchless control

- Blur or replace video conference backgrounds

- Gaze correction and audience analytics

- Detect other relevant objects and sounds

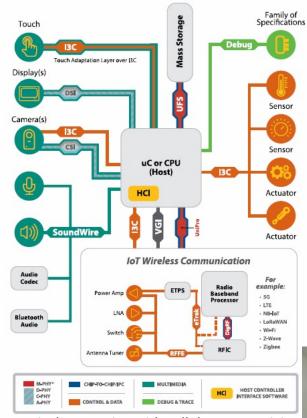

## Why MIPI

- MIPI was designed from the ground up to minimize power requirements while supporting high bandwidth and strict EMI requirements

- Many edge applications are battery operated

- MIPI CSI-2 is widely adopted for sensor applications

- MIPI D-PHY is the first and most widely adopted MIPI PHY today

Typical IoT Device with cellular connectivity using many MIPI specifications

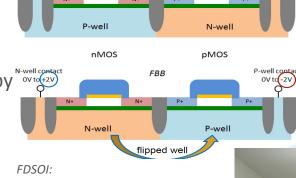

## Why FDSOI

FDSOI provides the right mix to achieve better performance, with lower power, at lower cost—without the need to move to more costly FinFET processes

Compared with bulk silicon, FDSOI provides additional flexibility, due to the programmability of body bias, resulting in higher performance and potential reduction in power and area

Body biasing allows trade-off between dynamic and leakage power resulting in lowest possible power consumption for workload and operating conditions

2. Reverse Body Bias (RBB) can be applied during stand-by mode to drastically reduce leakage current

3. FDSOI enables performance/frequency boost through Forward Body Bias (FBB)

No wonder FDSOI is widely adopted for IoT devices!

Fully-Depleted Silicon-On-

Planar process similar to bulk

Insulator

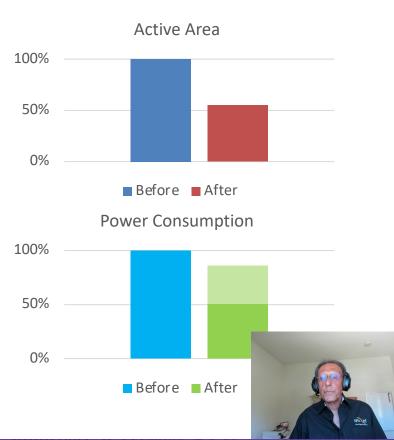

#### **Power and Area Saving Evaluation**

- By applying Forward Body Bias (FBB), device size was minimized while maintaining the same performance

- By adjusting the FBB and RBB based on PVT you can either reduce the area or the power or both

- Achievable power and area savings for FDSOI process:

- Active area reduction of ~55%

- Power reduction of 14-50% across PVT

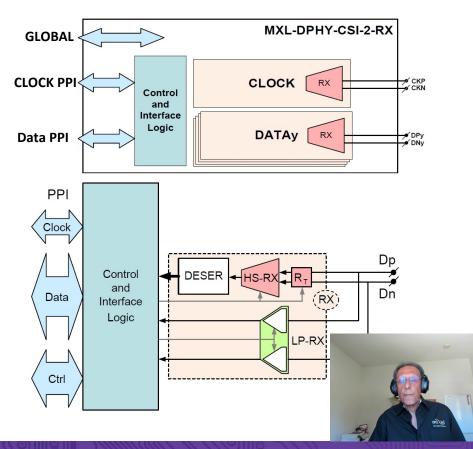

#### **Mixel MIPI Receiver IP**

- MIPI D-PHY CSI-2 RX IP

- Supports MIPI D-PHY v2.1 with backwards compatibility for v1.2 and v1.1

- High-speed transmitter running at 2.5Gbps/lane

- Low-power transmitter running at up to 80Mbps/lane

- 2 and 4 data lanes and 1 clock lane configurations

- Area optimized

- Achieved first time silicon success

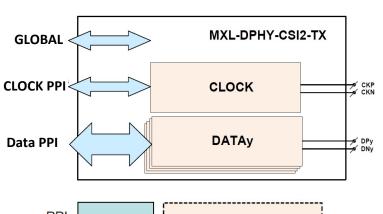

#### **Mixel MIPI Transmitter IP**

- MIPI D-PHY CSI-2 TX IP

- Supports MIPI D-PHY v2.1 with backwards compatibility for v1.2 and v1.1

- High-speed transmitter running at 2.5Gbps/lane

- Low-power transmitter running at up to 80Mbps/lane

- 4 data lanes and 1 clock lane

- Area optimized

- Achieved first time silicon success

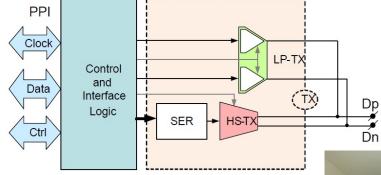

#### **Silicon Results**

MIPI D-PHY TX @ 1.5Gbps

MIPI D-PHY TX @ 2.5Gbps

#### **Mixel IP in FDSOI Processes**

| IP Name             | Features                                      | Node                         |

|---------------------|-----------------------------------------------|------------------------------|

| D-PHY Universal     | V1.2; 2.5Gbps; De-skew; loopback testability. | Silicon-Proven in<br>28FDSOI |

| D-PHY Universal     | 800Mbps; Ultra low power; Wearables, IoT.     |                              |

| D-PHY DSI TX        | 1.5Gbs; low Skew; Test modes.                 |                              |

| D-PHY CSI-2 RX      | 1.5Gbs; Test modes.                           |                              |

| LVDS TX             | 1.25Gbps; 4 Channel; 7 or 10 bits/channel     |                              |

| LVDS TX             | 1.25Gbps; 8 Channel; 7 or 10 bits/channel     |                              |

| LVDS/D-PHY TX Combo | 1.05Gbps; 4 Channel; Test modes.              |                              |

| LVDS/D-PHY TX Combo | 1.05Gbps; 8 Channel; Test modes.              |                              |

| D-PHY CSI-2 TX      | 2.5 Gbps/lane; 4 lanes                        | Silicon-Proven in 22FDX      |

| D-PHY CSI-2 RX      | 2.5Gbps/lane; 2 or 4 lanes                    |                              |

| D-PHY CSI-2 RX      | 2.5Gbps/lane; 2 or 4 lanes                    |                              |

#### **Mixel MIPI PHY Portfolio**

Industry leader in MIPI® interfaces and contributing member of the MIPI Alliance since 2006

- MIPI D-PHY first silicon-proven in 2008

- MIPI M-PHY® first silicon-proven in 2011

- MIPI C-PHY first silicon-proven in 2016

- Complete integrated solution includes PHY, controller, and platform

- Widest coverage of process nodes and foundries: silicon-proven in 11 different nodes and 8 different foundries

#### **Conclusion**

- Edge computing provides many benefits including the ability to make decisions in real time, with very low latency

- MIPI specifications are uniquely designed to enable low power, high bandwidth requirements of IOT & edge devices

- FDSOI provides high performance with lower power at lower cost

- Processors like Perceive Ergo enable AI processing at the edge to make connected devices smarter, resulting in lower latency, improved battery life, and better security

- Mixel MIPI PHY IP enables SoC designers to leverage the benefits of MIPI with silicon-proven designs in FDSOI, lowering project risk

# THANK YOU!

## REFERENCES & ADDITIONAL RESOURCES

- From Cloud to Edge

- A look at examples of IoT devices and their business applications in 2021

- What is edge computing? Everything you need to know

- Edge Intelligence Makes Smart Homes Truly Intelligent

- Autonomous Vehicles Drive Al Advances for Edge Computing

- Smart manufacturing and the IoT are driving the Industry 4.0 revolution

- Smart Manufacturing: Cloud vs. Edge Computing

- MIPI White Paper: Enabling the IoT Opportunity

- It's Time to Look at FDSOI Again