#### IF IT'S NOT MIPI, IT'S NOT MOBILE

### Let's Get Practical

How Can You Benefit from MIPI A-PHY

#### **Edo Cohen**

MIPI A-PHY Working Group Co-Chair Valens Semiconductor 13 October 2021

MIPI<sup>®</sup>, CSI-2<sup>®</sup>, DSI<sup>®</sup> and I3C<sup>®</sup> are registered trademarks of MIPI Alliance. A-PHY<sup>SM</sup>, C-PHY<sup>SM</sup>, CSI<sup>SM</sup>, D-PHY<sup>SM</sup>, DSI-2<sup>SM</sup>, MASS<sup>SM</sup> and PAL<sup>SM</sup> are service marks of MIPI Alliance.

$\mathsf{VESA}^{\circledast}$  is a registered trademark of the Video Electronics Standards Association.

### **A-PHY v1.0 Overview**

# **MIPI A-PHY Overview**

# MIPI A-PHY – Automotive Long-Reach PHY

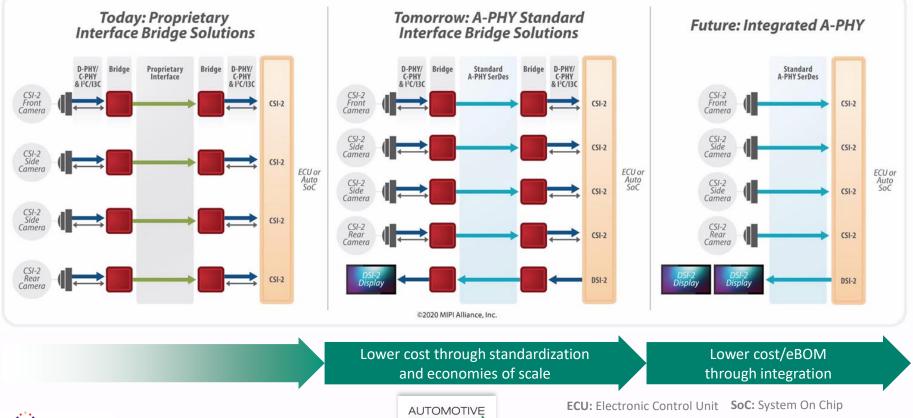

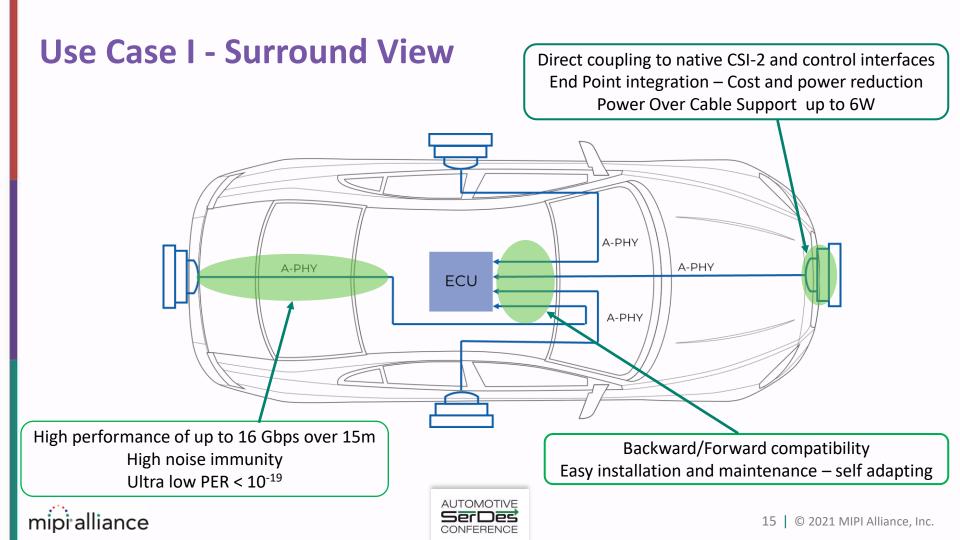

The first industry-standard *long-reach* asymmetric SerDes physical layer specification targeted for ADAS/ADS surround sensor applications and infotainment display applications

#### A-PHY v1.0 offers:

- Direct coupling to native CSI-2/DSI-2/DP-eDP protocols

- High performance of up to 16 Gbps over 10-15m

- High noise immunity, ultra low PER (< 10<sup>-19</sup>)

- Supports bridge-based and endpoint integration

- Support for automotive coax and STP\SPP channels

- Power over cable

#### **\*\*NEW\*\*** A-PHY v1.1 Enhancements:

- Increased support for lower cost legacy cables

- Double uplink data rate

- Star quad cable support, enabling dual downlink operation

ADAS: Advanced Driver Assistance System ADS: Autonomous Driving System SoC: System On Chip

### A-PHY v1.0 Performance- and Immunity-Based Profiles

#### Performance Variance and Scalability

• A-PHY scales up the bandwidth without changing the cables and connectors by increasing the PAM level

#### Noise Immunity (EMC RF Ingress) Variance

- Different OEMs have different requirements

- MIPI-conducted EMC tests at independent labs evaluating noise levels and shielding effects degradation after mechanical stress and aging

#### Two Performance / Noise Immunity Profiles

- Profile 1: Optimized for low cost/power implementations for lower gears with lower noise immunity and target PER <10<sup>-9</sup>

- Profile 2: Optimized for Vehicle Life-span, link robustness for all Gears with high noise immunity and target PER <10<sup>-19</sup>

#### Interoperability

- Full inter-profile interoperability

- A-PHY Device supporting Gear N (N could be 1–5) shall support all lower gears.

#### MIPI A-PHY v1.0 Performance

| <b>Downlink</b><br><b>Gear</b><br>Data Rate | Modulation | Modulation<br>Bandwidth<br>(GHz) | Max Net App<br>Data Rate<br>(Gbps) |  |

|---------------------------------------------|------------|----------------------------------|------------------------------------|--|

| G1<br>2 Gbps                                | NRZ-8B/10B | 1                                | 1.5                                |  |

| G2<br>4 Gbps                                | NRZ-8B/10B | 2                                | 3                                  |  |

| <b>G3</b><br>8 Gbps                         | PAM4       | 2                                | 7.2                                |  |

| <b>G4</b><br>12 Gbps                        | PAM8       | 2                                | 10.8                               |  |

| <b>G5</b><br>16 Gbps                        | PAM16      | 2                                | 14.4                               |  |

| Uplink<br>100Mbps                           | NRZ-8B/10B | 0.05                             | 55 Mbps                            |  |

# What Makes MIPI A-PHY So Robust and Efficient?

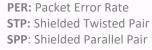

### **RTS + NBIC**

- **Time bounded** local PHY level retransmission.

- Only within a pre-defined "Overall Delay" (~6µs@G5)

- Local: Transparent to the upper Layers

- Local: Happens within a single A-PHY Hop

- Dynamic modulation for retransmitted packets with better error resistance

- Highly resilient

- Overcome large Thousands symbols-long error bursts

- Multiple 10s mV, instantly attacking NBI peaks

- High reliability → PER < 10<sup>-19</sup>

- Low overhead → 90% Net Data Rate

**RTS:** Re-Transmission Sub-Layer **N**

PMD: Physical Media Dependent PCS: Physical Coding Sub-Layer

NBI: Narrow Band Interferences

PCS: Physical Coding Sub-Layer

6 © 2021 MIPI Alliance, Inc.

**NBIC:** Narrow Band Interferences Canceller

### **A-Packet**

|                                   | A-Packet |                                  |               |                            |             |                                |                               |                           |                    |

|-----------------------------------|----------|----------------------------------|---------------|----------------------------|-------------|--------------------------------|-------------------------------|---------------------------|--------------------|

| A-Packet Header                   |          |                                  |               |                            |             |                                | A-Packet Payload              | A-Packet Tail             |                    |

| (                                 |          |                                  |               |                            |             |                                |                               |                           | ſ                  |

| 8-bit<br>Adaptation<br>Descriptor |          | 8-bit<br>Placement<br>Descriptor | 8-bit<br>TX-D | 8-bit<br>Target<br>Address | 8-bit<br>MC | 8-bit<br>Payload<br>Length (N) | 8-bit<br>PHY<br>Header<br>CRC | Payload (K Payload Bytes) | PHY Tail<br>CRC-32 |

- The A-Packet is structured to carry the Native Protocol data and all information that the A-PHY Data Link Layer requires to perform its functions efficiently.

- Downlink and uplink use the same packet structure.

- Structure optimized supporting multiple protocols aggregation with minimal overhead and latency

- The A-Packet Header contains all required information (e.g., QoS, Priority, Destination, Protocol Type).

- The A-Packet structure:

- Header 8 Byte including MC (Message Counter)

- Payload

- Tail 4 Byte (CRC-32)

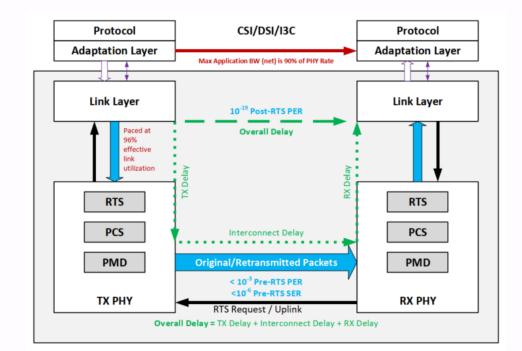

## **A-PHY Interconnect**

- A-PHY is a single lane, point-to-point, serial communication technology

- Support for multiple cable types SDP/Coax

- Power over cable support

mipi

• Up to 15m with 4 inline connectors

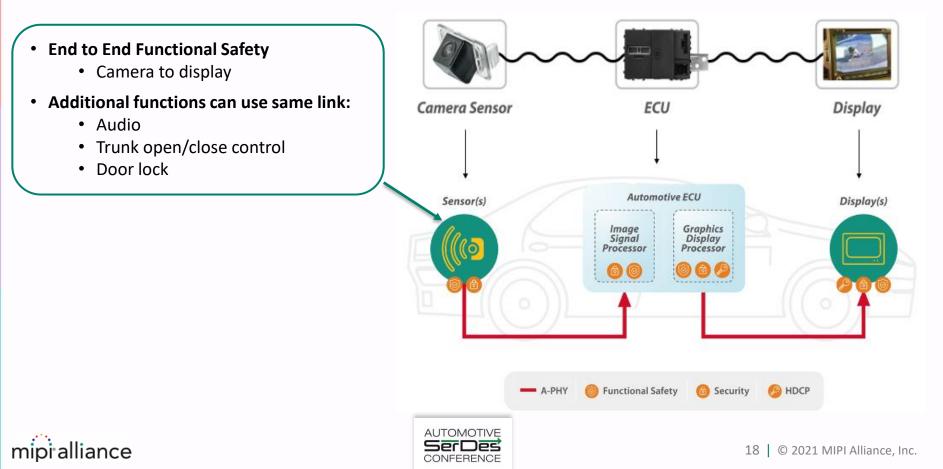

# **A-PHY Functional Safety Features**

- A-PHY packets are end-to-end protected as recommended in ISO-26262:2018:

- CRC-32 for each packet, providing a Hamming-Distance of more than 3

- Message Counter that is 8 bits wide

- Timeout monitoring is fulfilled by the Keep-Alive function

- The above measures are necessary to argue a high diagnostic coverage for a communication bus, per Table D.6 in ISO 26262-5:2018

- All other functional safety features necessary to fulfill the required system-level safety goal with ASIL are expected to be managed by upper layers

A-PHY's tunnels, end-to-end, all the protection elements, allowing both Safety and Security (SPDM).

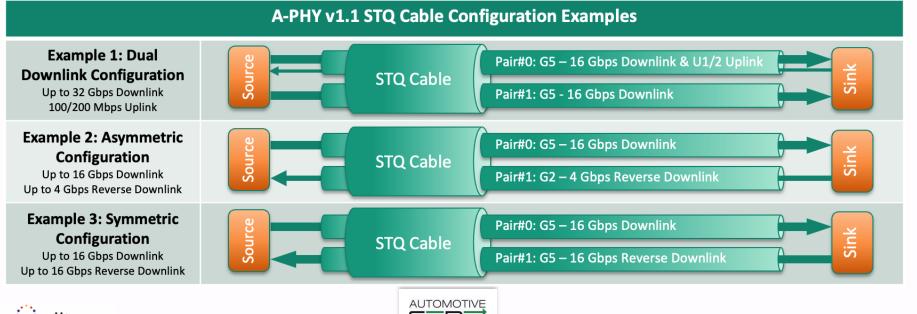

### What's Coming in A-PHY v1.1

#### A-PHY v1.1 enhancements:

- 200 Mbps double rate uplink (U2)

- Optional PAM4 modes for G1 & G2

- Adds STQ cable support (see next slide)

#### **Enhanced** Performance Variance and Scalability

Expands PAM4 encoding to lower gears, reducing the operating signal rate of these gears and allowing implementation of A-PHY using lower cost legacy cables and connectors.

#### Same High Noise Immunity (EMC RF Ingress)

Supports same high noise immunity with an ultra-low Packet Error Rate  $(< 10^{-19}) \rightarrow$  built for vehicle life span support

#### **Interoperability and Compatibility**

- A-PHY v1.1 backward compatible with v1.0

- A-PHY v1.0 forward compatible with v1.1

alliance

A-PHY guarantees full inter-profile interoperability; devices will support all the various gears below them

CONFERENCE

#### MIPI A-PHY Performance

A-PHY v1.1 enhancements shown in orange

| <b>Downlink</b><br><b>Gear</b><br>Data Rate | Modulation            | <b>Modulation</b><br><b>Bandwidth</b><br>(GHz) | Max Net App<br>Data Rate<br>(Gbps) |  |

|---------------------------------------------|-----------------------|------------------------------------------------|------------------------------------|--|

| G1                                          | NRZ-8B/10B            | 1                                              | 1.5                                |  |

| 2 Gbps                                      | PAM4 (Optional)       | 0.5                                            | 1.8                                |  |

| G2                                          | NRZ-8B/10B            | 2                                              | 3                                  |  |

| 4 Gbps                                      | PAM4 (Optional)       | 1                                              | 3.6                                |  |

| <b>G3</b><br>8 Gbps                         | PAM4                  | 2                                              | 7.2                                |  |

| <b>G4</b><br>12 Gbps                        | PAM8                  | 2                                              | 10.8<br>14.4                       |  |

| <b>G5</b><br>16 Gbps                        | PAM16                 | 2                                              |                                    |  |

|                                             |                       |                                                |                                    |  |

| <b>Uplink</b><br>Gear<br>Data Rate          | Modulation            | <b>Modulation</b><br><b>Bandwidth</b><br>(MHz) | Max Net App<br>Data Rate<br>(Mbps) |  |

| <i>U1</i><br>100 Mbps                       | NRZ-8B/10B            | 50                                             | 55                                 |  |

| <b>U2</b><br>200 Mbps                       | PAM4-8B/10B           | 50                                             | 125                                |  |

|                                             | 10   © 2021 MIPI Alli |                                                |                                    |  |

Inc.

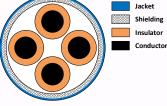

# A-PHY v1.1: Adds Support for STQ Cables

- Supports Star Quad (STQ) shielded dual differential pair (i.e., 4 conductor) cables and High-Speed Data (HSD) connectors.

- Referred to as "Q-Port" within the A-PHY working group.

mipralliance

• Efficient size, cost and weight compared to two separate Shielded Differential Pair (SDP) cables

CONFERENCE

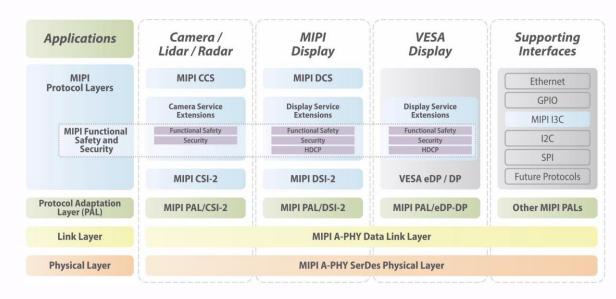

### A-PHY is the Foundation of MIPI Automotive SerDes Solutions (MASS)

- Direct coupling to native MIPI protocols (i.e., CSI-2, DSI-2)

- End to End Functional Safety

- End to End Security (WIP)

- Multiple supporting interfaces:

- I2C

- GPIO

- Ethernet

- MIPI I3C (WIP)

- SPI (WIP)

alliance

# First MIPI A-PHY Compliant Chipset – Available

- MIPI A-PHY V1.0 compliant system

- Up to 8Gbps Downlink (G1-G3)

- ISO-26262, ASIL-B

- Serializer

- CSI-2 input over D-PHY

- 4 Data Lanes up to 2.5Gbps per lane

- 16 Virtual Channels

- Control I2C, GPIO

- Quad De-serializer

- 4 x A-PHY Ports (G3)

- 2 x CSI-2 output over D/C-PHY

- D-PHY 4 Data Lanes up to 2.5Gbps per lane

- C-PHY 2 Data Lanes up to 5.7 Gsps per lane

- Control I2C, GPIO

### **Example Use Cases**

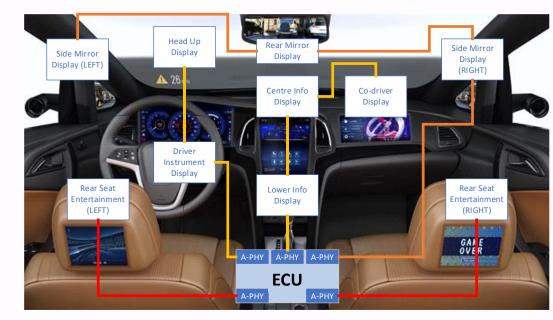

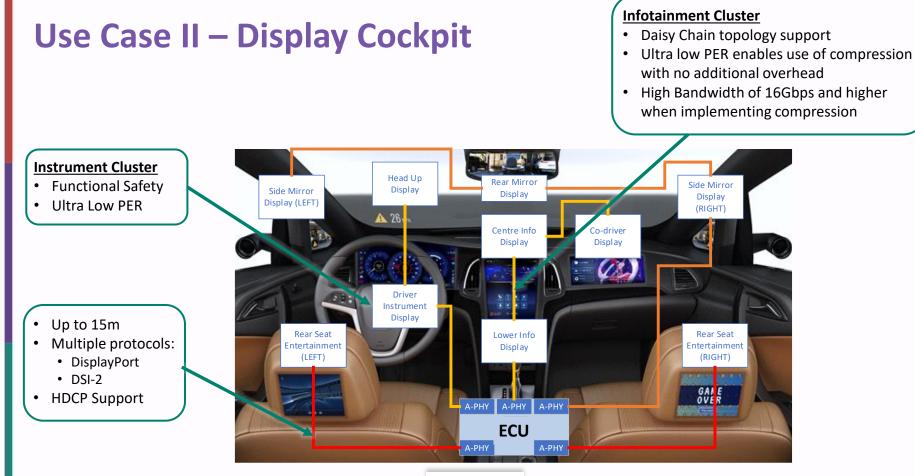

### **Use Case II – Display Cockpit**

| Disp | olay Type                    | Number | Size<br>(Inches) | Example<br>Resolution | Net Data<br>Throughput<br>(Gbps) |

|------|------------------------------|--------|------------------|-----------------------|----------------------------------|

| 1    | Driver Instrument Display    | 1      | 12.3             | 3840x1440             | 8.4                              |

| 2    | Center Information Display   | 1      | 12.3             | 3840x2160             | 12.6                             |

| 3    | Lower Control Display        | 1      | 12.4             | 3840x2160             | 12.6                             |

| 4    | Co-Driver Display            | 1      | 12.3             | 3840x2160             | 12.6                             |

| 5    | Side Digital-Mirror Displays | 2      | 7                | 1280x800              | 1.5                              |

| б    | Heads-Up Display             | 1      | 3.1              | 850x480               | 0.6                              |

| 7    | Rear Seat Entertainment      | 2+     | 12.5             | 3820x2160             | 12.6                             |

| 8    | Rear Digital-Mirror Display  | 1      | 9.7              | 1280x320              | 0.75                             |

#### Notes

- Bandwidth calculation assumes 24b@60Hz VESA CVT 1.2 timing

- VESA DSC Compression can be applied with no additional overhead can support links of up to 48Gbps (~43Gbps net data)

- A-PHY V1.1 Dual Downlink (32Gbps) with compression can support up **96Gbps** (~86Gbps net data).

- A-PHY V1.1 provides flexibility for the return channel

### mipialliance

### **Use Case III – Digital Backup Camera**

## Summary

# Summary

- Established ecosystem with multiple vendors working on A-PHY compliant chipsets

- First samples will be available by EOY2021

- Clear and forward-looking roadmap and planning

- A-PHY v1.0 Released in 2020

- A-PHY v1.1 Targeted for release in 2021

- A-PHY v2.0 Work has started in the MIPI A-PHY Working Group

- New PALs Expending support for command-and-control interfaces, such as SPI and Ethernet

- Supporting multiple advanced use cases with clear advantages of an industry standard

- "Error Free" links

- Seamless integration

- Interoperability and forward compatibility

# **MIPI Automotive Resources**

MIPI ALLIANCE EDUCATION

### Automotive Workshop

17 November 2021

For automotive developers, system architects and engineering managers who are focused on the design, development, integration and test of next-generation automotive E/E architectures. Will cover:

- MIPI Automotive SerDes Solutions (MASS)

- Display and sensor (camera/lidar/radar) stacks

- Functional safety, security and data protection

- MIPI A-PHY implementation, system modelling and test.

https://www.mipi.org/events/2021-automotive-workshop

Information on A-PHY can be found at:

- MIPI A-PHY Specification Homepage

- MIPI White Paper: Introduction to MASS

### **Thank You**