# mipi<sup>®</sup> DEVCON MIPI ALLIANCE DEVELOPERS CONFERENCE

# Amit Ashara, Saminah Chaudhry Texas Instruments

Enabling Simpler Design with MIPI I3C<sup>®</sup> in different End-Equipment Applications

20-21 SEPTEMBER

MIPI.ORG/DEVCON

# Agenda

2022

- I3C motivation

- I3C applications in

- Servers

- Communications equipment

- Consumer electronics

- Automotive

- Industrial

- Additional resources

# **I3C Motivation**

2022

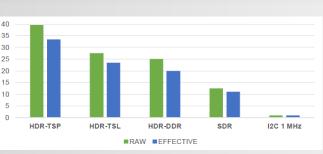

### Fast efficient communication channel

Source: MIPI I3C Specification v1.1.1, page 3

I3C vs. I<sup>2</sup>C FM+ Data Blocks Bit Rates in Mbps (12.5 MHz Clock)

- Multidrop SDA/SCL 2-wire interface

- 12.5 MHz max clock rate

- 1.2V-3.3V voltage supported

- Physical layer CMOS I/O compatible

- Dynamic switch between pullup/push pull/Hi-Z

- SDR (Single Data Rate) 12.5 Mbps

- HDR (High Data Rate) Modes for higher throughput (HDR-DDR, HDR-TSL, HDR-TSP, HDR-BT)

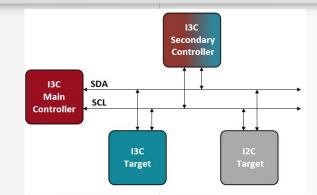

# System management, standardization & backward compatibility

- Device Roles: I3C primary & secondary Controllers

- Dynamic address assignment (including group addressing)

- Standardized commands for bus management, configuration and control

- Backwards compatible allowing mixed bus operation (I<sup>2</sup>C and I3C)

- Broadcast & direct messages

- Error detection & recovery, parity, CRC

Advance functions

- Target reset

- In-band interrupt (IBI)

- Hot-join

- Timing control

- Energy efficiency

#### MIPI.ORG/DEVCON

# M@BILE & BEY@ND

#### © 2022 MIPI Alliance, Inc. 3

# mipi<sup>®</sup> DEVCON

MIPI ALLIANCE DEVELOPERS CONFERENCE

# **I3C Applications in Different End Equipment**

MIPI.ORG/DEVCON

MOBILE & BEYOND

© 2022 MIPI Alliance, Inc.

# **I3C Applications in Servers-bus Switching**

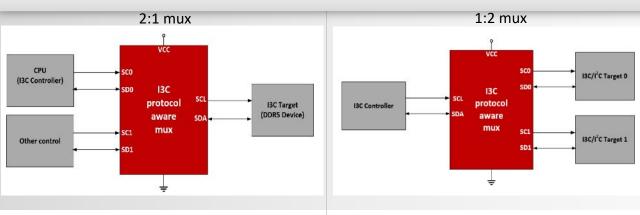

### I3C protocol aware multiplexing/switching applications

#### <u>Use case:</u>

2022

I3C multiplexing used in various motherboard applications:

Switching for the CPU and BMC to the DDR5 device; Either CPU or BMC can be selected as active controller which has control of the Target port as well as the I3C Target Device

#### Use case:

I3C Target Devices that share the same address can use the I3C protocol aware multiplexer to prevent Target address conflicts

### I3C features enabling simpler design

### Target reset:

- Allows the controller to reset one or more selected targets

- Useful in avoiding deadlocks on the bus due to an unresponsive device

- Avoids extra dedicated wires for reset

#### In-band interrupt:

- Device driven in-band interrupts handled through I3C Bus

- Fast and efficient asynchronous data acquisition, and event processing

- Avoids extra dedicated wires or inefficient polling mechanism

#### High speed:

I3C SDR and HDR Modes provide faster bus transactions, reducing CPU cycles

#### MIPI.ORG/DEVCON

# mipi **DEV**CON

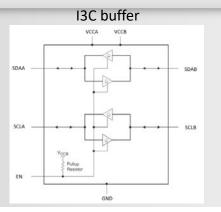

# **I3C Applications in Servers-buffer**

## **I3C buffering applications**

#### <u>Use case:</u>

2022

- I3C applications in server systems deal with higher bus capacitance than the max limit (50pF) in MIPI I3C spec

- Buffering I3C signal using I3C buffer allows connection of multiple I3C Targets to the downstream bus (especially with long traces)

### Typical Application on a backplane

#### Use case:

- The I3C buffer can be placed on the I/O peripheral card and connects the I3C Devices on the card to the backplane safely upon a hot join event

- Placing a bus buffer on the edge of each card isolates the card capacitance from the backplane

# I3C features enabling simpler design

### Hot-join:

- I3C Targets are allowed to join the bus after it has already been configured

- Improved power management and energy savings:

- Selective powering on and off of system sub-units

- Wake-up I3C Targets only when needed

- Ideal for I3C Devices:

- Mounted on the same board, but de-powered until needed

- Mounted on module/board that is physically inserted after

I3C Bus has already been configured

#### MIPI.ORG/DEVCON

# **I3C Applications in Servers-sensing**

### **I3C sensing applications**

#### Typical application on DIMM and SSD PMIC 1001xxx **I3C Local Bus** DRAM DRAM DRAM DRAM TS0 TS1 DRAM DRAM 0110xxx 0010xxx DRAM DRAM SPD 1010xxx **I3C Host Bus**

### Use case:

2022

- Higher DDR-5 memory data rates, require faster, low-latency control plane

- Integrated interrupt management, store and recall of DIMM properties and transactions to reduce system initialization time

## I3C features enabling simpler design

### I3C high speed:

- I<sup>2</sup>C speed has become limiting, as amount of data increases on the bus

- I3C SDR and HDR Modes allows faster management transactions for modules that require frequent accesses

#### In-band interrupt:

- Device driven in-band interrupts handled through I3C Bus

- Fast and efficient event processing

- Avoids extra dedicated wires or inefficient polling mechanism

### MIPI.ORG/DEVCON

# MOBILE & BEYOND

# mipi **DEV**CON

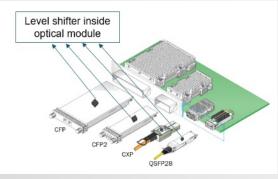

# **I3C Applications in Communications Equipment**

**I3C** level

shifter

Octal small factor

pluggable (OSFP)

13C

Controller

optical module

⊥0.1 µF

### **I3C translation applications in optical transceivers**

#### <u>Use case:</u>

2022

- Optical modules (QSFP, CFP, OSFP etc.) all feature 3.3V I/O interfaces (I<sup>2</sup>C, I3C, MDIO) at the connector and implement a micro/ASIC that communicates across these interfaces

- Forward-looking micros moving towards smaller geometry, lower voltage (1.2V/1.8V IO voltage)

3.3 V

- OSFP pluggable optical modules use I3C (SDR at 12.5Mhz) and I<sup>2</sup>C as optical interface with 400 Gbps (8x50G or 4x100G) support

- I3C level translator provides translation between host controller at 3.3V and OSFP module at I3C speeds and low IO voltage

# I3C features enabling simpler design

## I3C high speed:

1.2 V

0.1 µF

**I3C Target**

Devices

- I<sup>2</sup>C speed has become limiting, as amount of data increases on the bus

- I3C SDR Mode allows faster management transactions for modules that require frequent accesses

- High I3C speed and low latency is used to program modules and additional high-speed telemetry

### Backwards compatibility to I<sup>2</sup>C:

Existing I<sup>2</sup>C devices can be connected to an I3C Bus, but still supports the ability to switch to a higher data rate for communication at higher speeds between compliant I3C Devices

#### MIPI.ORG/DEVCON

# MOBILE & BEYOND

# **I3C Applications in Consumer Electronics & Automotive**

### **I3C IO expansion applications**

#### <u>Use case:</u>

2022

- Using an IO expander, host controller can expand the IO to multiple peripheral or Target Devices

- I3C IO expander enhances the I/O performance in terms of speed and energy consumption. In applications where multiple sensors are used in a very limited physical space and with stringent power restrictions, I3C provides a shared 2-wire interface to connect sensors and simple UI components such as LEDs and buttons

## I3C features enabling simpler design

#### Low energy consumption:

- SCL being push-pull only and SDA working in push-pull most of the time improves energy efficiency ideal for wearables, PE applications

- I3C can save considerable device power through higher data rates (because the device can be put back to sleep sooner)

#### Other features:

- In-Band Interrupt (IBI) reduces number of GPIO wires on microcontroller, as number of sensors increase on the mobile devices

- Enables active sleep mode, with sensors waking the application processor only when required

- Reduced system cost with low pin count (No interrupt or reset pins)

### MIPI.ORG/DEVCON

# mipi **DEV**CON

# **I3C Applications in Industrial**

### **I3C Test and measurement applications**

#### <u>Use case:</u>

2022

- Increased throughput from test and measurement equipment requires more integration of sensors in the system, that collect data and allow host controller to process real time inputs.

Slower data rates limit capabilities of the system to aggregate mission-critical inputs

- Safety systems in place requires host to dedicate interrupt lines and run prioritization based on conflicting interrupts from sensors across the system

### I3C features enabling simpler design

#### Higher Data Rates

I3C SDR and HDR-DDR raw data rates of 12.5 Mbps and 25 Mbps allow host to query data with low latencies.

### Other features:

- In-Band Interrupt (IBI) reduces number of GPIO wires on microcontroller, as number of sensors increase on the test system

- Dynamic address assignments allows host controller to re-prioritize interrupts based on process criticality

#### MIPI.ORG/DEVCON

# MOBILE & BEYOND

# Summary

2022

- MIPI I3C<sup>®</sup> Bus allows applications to leverage well standardized capabilities to expand and scale.

- 2-Pin configuration with integrated IBI and Hot-Join indication, reduces requirement on scaling Host Controllers as application scales.

- Reduction in energy consumption for faster bus traffic not only improves battery life in consumer electronics, but also enables "Green Technology" beyond into Industrial and Automotive sectors.

Application brief: <u>I3C – Next Generation Serial Communication</u> <u>Interface</u> (<u>https://www.ti.com/lit/an/scpa066/scpa066.pdf</u>)

Application brief: Enhance Thermal Sensing Performance With I3C Bus (<u>https://www.ti.com/lit/pdf/snia045</u>)

2022

# mipi<sup>®</sup> DEVCON

MIPI ALLIANCE DEVELOPERS CONFERENCE

# THANK YOU!

20-21

SEPTEMBER

()

MIPI.ORG/DEVCON

MOBILE & BEYOND

© 2022 MIPI Alliance, Inc.

# mipi<sup>®</sup> DEVCON

MIPI ALLIANCE DEVELOPERS CONFERENCE

# 20-21 september 2022

#### MIPI.ORG/DEVCON

MOBILE & BEYOND

© 2022 MIPI Alliance, Inc.