# MIPI ALLIANCE DEVELOPERS CONFERENCE

Edo Cohen, Valens Semiconductor Raj Kumar Nagpal, Synopsys Inc. George Wiley, Qualcomm Incorporated Kirill Dimitrov, Western Digital

# What's New and Coming Up on the MIPI PHY Roadmap

20-21 SEPTEMBER 2022

MIPI.ORG/DEVCON

M@BILE & BEY@ND

### Agenda

2022

- MIPI A-PHY<sup>®</sup> Future Plans

- MIPI D-PHY<sup>sm</sup> Future Plans

- MIPI C-PHY<sup>sm</sup> Future Plans

- MIPI M-PHY<sup>®</sup> Status/Future Plans

#### **MIPI PHY's Ecosystems**

#### **MIPI Multimedia Specifications**

MOBILE & BEYOND

MIPI.ORG/DEVCON

2022

### mipi DEVCON

MIPI ALLIANCE DEVELOPERS CONFERENCE

### **MIPI A-PHY® Future Plans**

MIPI.ORG/DEVCON

MOBILE & BEYOND

20-21

SEPTEMBER

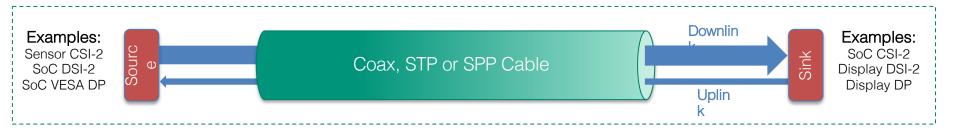

### What is A-PHY?

The first industry-standard *long-reach* asymmetric SerDes physical layer specification targeted for ADAS/ADS surround sensor applications and infotainment display applications

#### A-PHY v1.0 offers:

2022

- Direct coupling to native CSI-2/DSI-2/DP-eDP protocols

- High performance of up to 16 Gbps over 10-15m

- High noise immunity, ultra low PER (< 10<sup>-19</sup>)

- Supports bridge-based and endpoint integration

- Support for automotive coax and STP channels

- Power over cable

- Built-in Functional Safety according to ISO 26262

#### A-PHY v1.1 Enhancements:

- Increased support for lower cost legacy cables

- Double uplink data rate

- Star quad cable support, enabling dual downlink operation

PER: Packet ErrorADAS: Advanced Driver Assistance SystemBateSTP: Shielded Twisted PairADS: Autonomous Driving SystemSPP: Shielded Parallel PairSoC: System On Chip

#### MIPI.ORG/DEVCON

#### M@BILE & BEY@ND

### **A-PHY Feature Roadmap**

| Category               | Feature                                                                  | v1.0                     | v1.1 <sup>(2)</sup>      | V2.0                     | Next                     |

|------------------------|--------------------------------------------------------------------------|--------------------------|--------------------------|--------------------------|--------------------------|

|                        | Board Adoption                                                           | Q3 20                    | Q4 21                    | Q2 23                    | 24-25                    |

|                        | Coax Channel 15 meter – 4-inline connectors                              | ✓                        | ✓                        | TBD                      | TBD                      |

| Channels               | STP / SPP Channel 10 meter – 4 inline connectors                         | ✓                        | ✓                        | TBD                      | TBD                      |

|                        | STQ 10 meter – 4 inline connectors (2 differential pairs)                | -                        | $\checkmark$             | TBD                      | TBD                      |

| Max Downlink Data Rate | Single Lane Downlink                                                     | 16Gbps                   | 16Gbps                   | 32Gbps                   | >48Gbps                  |

|                        | Dual Lane Downlink                                                       | -                        | 32Gbps                   | 64Gbps                   | ~100Gbps                 |

| Max Uplink Data Rate   | Uplink                                                                   | 100Mbps                  | 200Mbps                  | 1.6Gbps                  | TBD                      |

| Power Over Cable       | Power over Coax and Power over Data Line – Max power delivery            | 6W                       | 6W                       | 10W <sup>(1)</sup>       | TBD <sup>(1)</sup>       |

|                        | RF Ingress (ISO 11452-2)                                                 | ✓                        | √                        | √                        | ✓                        |

|                        | Bulk Current Injection (ISO 11452-4)                                     | ✓                        | ✓                        | ✓                        | ✓                        |

| EMC Requirements       | Fast Transient (ISO 7637-2/3)                                            | ✓                        | ✓                        | ✓                        | ✓                        |

|                        | Alien Cable bundle cross talk                                            | √                        | √                        | √                        | ✓                        |

|                        | Car Noise                                                                | √                        | $\checkmark$             | ✓                        | √                        |

|                        | Modulations: NRZ, PAM4, PAM8, PAM16                                      | √                        | $\checkmark$             | √                        | √                        |

|                        | Just-In-Time-Canceller & Retransmission                                  | ✓                        | ✓                        | ✓                        | ✓                        |

| Advanced features      | Packet Error Rate                                                        | <b>10</b> <sup>-19</sup> | <b>10</b> <sup>-19</sup> | <b>10</b> <sup>-19</sup> | <b>10</b> <sup>-19</sup> |

|                        | Max Link Latency @ G5 (16Gbps)                                           | ~6uSec                   | ~6uSec                   | TBD                      | TBD                      |

|                        | Functional Safety (ISO 26262) – Message Counter, CRC, Timeout monitoring | ✓                        | $\checkmark$             | ✓                        | ✓                        |

| Data Link Layer        | Local Functions, Multi-Port Functions, Network Functions                 | ✓                        | ✓                        | ✓                        | $\checkmark$             |

|                        | BIST                                                                     | ✓                        | $\checkmark$             | ✓                        | $\checkmark$             |

|                        | Clock Forwarding Service                                                 | ✓                        | √                        | ✓                        | ✓                        |

|                        | Timebase Service                                                         | -                        | √                        | ✓                        | ✓                        |

MOBILE & BEYOND

Note:

2022

(1) Power over cable will be defined in the PoA specification (separated from A-PHY specification)

(2) A-PHY v1.1.1 will replace v1.1 with inclusive terminology update

#### MIPI.ORG/DEVCON

### **A-PHY Feature Roadmap**

| Category               | Feature                                      | v1.0 | v1.1 | V2.0 | Next |

|------------------------|----------------------------------------------|------|------|------|------|

| Control and Management | ACMD – A-PHY Control and Management Database | ✓    | ✓    | ✓    | ✓    |

|                        | ACMP – A-PHY Control and Management Protocol | √    | ✓    | √    | ✓    |

|                        | ACMPn – additional ACMP modes (e.g. CCISE)   | -    | ✓    | ✓    | ✓    |

#### **A-PHY PAL Roadmap**

| Category                  | Feature        | A-PHY v1.0          | A-PHY v1.1   | A-PHY Next |

|---------------------------|----------------|---------------------|--------------|------------|

| A-PHY                     | Board Adoption | Q3 20               | Q4 21        | ~2022/23   |

|                           | PAL/CSI-2      | v1.0                | v1.1 (Q1/22) |            |

|                           | PAL/DSI-2      | v1.0                |              |            |

|                           | PAL/eDP-DP     | v1.0                |              |            |

| Protocols Adaption Layers | PAL/GPIO       | v1.0                |              |            |

| Protocols Adaption Layers | PAL/I2C        | v1.0 <sup>(1)</sup> |              |            |

|                           | PAL/Ethernet   |                     | v1.0 (Q1/22) |            |

|                           | PAL/I3C        |                     | TBD          |            |

|                           | PAL/SPI        |                     | v1.0 (Q3/22) |            |

MOBILE & BEYOND

Note:

2022

(1) PAL/I2C v1.0.1 will replace v1.0 with inclusive terminology update

#### MIPI.ORG/DEVCON

mipi<sup>DEVCON</sup>

### **A-PHY-Based Zonal Architecture**

Simplification of zonal ECU

2022

- Low computing overhead

- Lower protocol overhead Maintain native protocols for MIPI CSI-2 (e.g., camera) or Ethernet (e.g., lidar)

- Designed for ultra-low PER at high noise environment for the entire lifespan of the vehicle

- Future-looking design and easy migration path

- Scalable downlink speed from 2Gbps to 64Gbps over a single cable

- Flexible and rich protocol support

- Layered security scheme supporting variety of use cases

- Embedded functional safety

- Guaranteed interoperability and backward/forward compatibility

#### VCON

#### MOBILE & BEYOND

MIPI.ORG/DEVCON

### mipi DEVCON

MIPI ALLIANCE DEVELOPERS CONFERENCE

### **MIPI D-PHY<sup>sm</sup> Future Plans**

MIPI.ORG/DEVCON

MOBILE & BEYOND

20-21

SEPTEMBER

#### mipi DEVCON

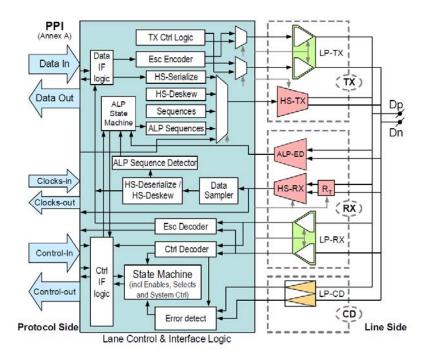

### What is D-PHY?

2022

- D-PHY is a Physical Layer targeted for Camera and Display applications.

- D-PHY is already in many mobile devices interfacing Camera and Display modules.

- D-PHY is targeted for short to medium reach applications.

### **D-PHY Feature Roadmap**

| Category          | Feature                                  | v1.0         | v1.1         | v1.2          | v2.0         | v2.1         | v2.5         | v3.0         |

|-------------------|------------------------------------------|--------------|--------------|---------------|--------------|--------------|--------------|--------------|

|                   | Board Adoption                           | 4Q 09        | 4Q 11        | 3Q 14         | 1Q 16        | 1Q 17        | 3Q 19        | 3Q 21        |

| Symbol Rate       | Standard Channel                         | 1            | 1.5          | 2.5           | 4.5          | 4.5          | 4.5          | 9            |

| (Gbps/Lane)       | Short Channel                            |              |              |               |              | 6.5          | 6.5          | 11           |

|                   | Basic De-emphasis                        |              |              |               | $\checkmark$ | √            | √            | $\checkmark$ |

| Increased         | Calibration                              |              |              | $\checkmark$  | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ |

| Symbol Rate       | Additional UI Jitter (RCLK jitter) specs |              | $\checkmark$ | $\checkmark$  | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ |

|                   | Rx Equalization                          |              |              |               |              |              |              | $\checkmark$ |

| Power Reduction   | Unterminated Mode                        |              |              |               | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ |

| Power Reduction   | Reduced Amplitude "LVLP" Mode option     |              |              |               |              | ✓            | √            | $\checkmark$ |

| LP Mode           | Alternate Low-Power Mode                 |              |              |               |              |              | $\checkmark$ | $\checkmark$ |

|                   | 16-bit/32-bit PPI                        |              |              |               | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ |

|                   | Optical Interconnect                     |              |              |               | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ |

| Enhanced          | HS Reverse Mode                          | $\checkmark$ | $\checkmark$ | $\checkmark$  | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ |

| Function          | PHY Generated/Detected Packet Delimiter  |              |              |               |              | $\checkmark$ | $\checkmark$ | $\checkmark$ |

|                   | Fast Lane Turnaround                     |              |              |               |              |              | $\checkmark$ | $\checkmark$ |

|                   | 4m channel support, for IoT use cases    |              |              |               | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ |

| Protocol<br>Specs | MIPI CSI-2®                              |              |              | v1.2/<br>v1.3 |              | v2.0         | v3.0         | v4.0         |

|                   | MIPI DSI-2 <sup>™</sup>                  | -            | -            | v1.1/<br>v1.0 | v2.0         | -            | -            | -            |

MIPI.ORG/DEVCON

2022

### **D-PHY Feature Roadmap**

| Category                   | Feature                                  | v3.0         | v3.5 FC | v3.5 EC<br>(Optional)     | v4.0 EC<br>(Tentative) |

|----------------------------|------------------------------------------|--------------|---------|---------------------------|------------------------|

|                            | Board Adoption                           | 3Q 21        |         |                           |                        |

| Symbol Rate<br>(Gbps/Lane) | Standard Channel                         | 9            | 9       | 9<br>Bands B1, B2, B3, B4 | TBD                    |

| (                          | Short Channel                            | 11           | 11      | Same as above             | TBD                    |

|                            | Basic De-emphasis                        | √            | √       | √                         | $\checkmark$           |

| Increased                  | Calibration                              | $\checkmark$ | √       | √                         | $\checkmark$           |

| Symbol Rate                | Additional UI Jitter (RCLK jitter) specs | $\checkmark$ | √       | √                         | $\checkmark$           |

|                            | Rx Equalization                          | ✓            | √       | ✓                         | $\checkmark$           |

| Power Reduction            | Unterminated Mode                        | $\checkmark$ | √       | Х                         | TBD                    |

| Power Reduction            | Reduced Amplitude "LVLP" Mode option     | ✓            | √       | ✓                         | $\checkmark$           |

| LP Mode                    | Alternate Low-Power Mode                 | $\checkmark$ | ✓       | Х                         | TBD                    |

|                            | 16-bit/32-bit PPI                        | ✓            | ✓       | √                         | $\checkmark$           |

|                            | Optical Interconnect                     | ✓            | ✓       | √                         | $\checkmark$           |

| Enhanced                   | HS Reverse Mode                          | ✓            | ✓       | Х                         | TBD                    |

| Function                   | PHY Generated/Detected Packet Delimiter  | ✓            | √       | √                         | $\checkmark$           |

|                            | Fast Bus Turnaround                      | ✓            | ✓       | Х                         | TBD                    |

|                            | 4m channel support, for IoT use cases    | ✓            | √       | √                         | $\checkmark$           |

| Protocol                   | CSI-2                                    | v4.0         |         |                           |                        |

| Specs                      | DSI-2                                    | v2.0         | v2.1    | v2.1                      | v3.0                   |

MIPI.ORG/DEVCON

2022

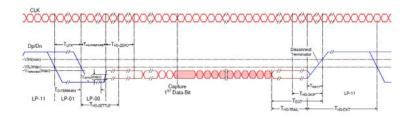

### **Specification under development phase**

D-PHY 3.5 include

2022

- Supports an optional Embedded Clock configuration.

- Embedded clock configuration has better EMC compliance and provides additional lane for data communication. Improves total data throughput.

- Embedded Clock mode supports up to 9 Gbps.

- Forwarded Clock configuration is carried forward from D-PHY 3.0.

- Forwarded Clock mode, fully backward compatible to D-PHY 3.0.

- ALP mode not supported in Embedded Clock mode.

- Support of 4 meter of channel for IOT applications.

- Targeted for Camera and Display protocols.

### **Overall possibilities**

2022

- Future plans of D-PHY 4.0 include

- Taking data rates to around 18 to 20 Gbps.

- Still keeping it NRZ.

- LP model to be removed. ALP mode to be primary mode.

- Support mid length around 4 meter of channel for IOT applications.

- Will not be fully backward compatible to D-PHY 3.5.

- Will be targeted for Camera and Display protocols.

### mipi DEVCON

MIPI ALLIANCE DEVELOPERS CONFERENCE

### **MIPI C-PHY<sup>sm</sup> Future Plans**

MIPI.ORG/DEVCON

MOBILE & BEYOND

20-21

SEPTEMBER

2022

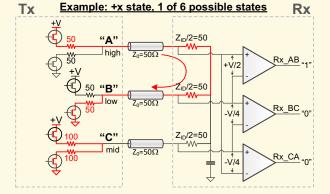

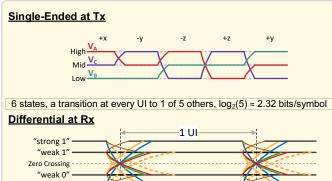

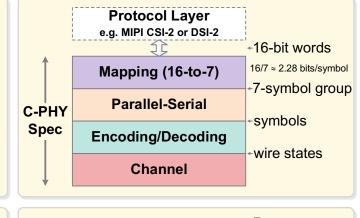

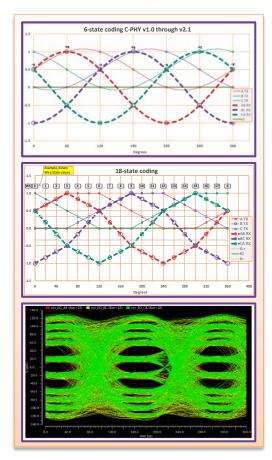

#### **Benefits of 3-Phase Coding**

• High bit rate: 2.28x sym. rate

mipi<sup>DEVCON</sup>

- Low power consumption

- Low signal toggle rate

- No clock signal emissions

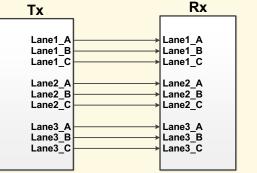

- Fewer Lanes required, fewer connections in a system

- Flexibility to assign Lanes to a specific camera or display Link

#### MIPI.ORG/DEVCON

"strong 0"

#### MOBILE & BEYOND

#### 2022

#### **C-PHY Feature Roadmap**

| Category          | Feature                                                      | v1.0  | v1.1         | v1.2         | v2.0         | v2.1         | v3.0         |

|-------------------|--------------------------------------------------------------|-------|--------------|--------------|--------------|--------------|--------------|

|                   | Board Adoption                                               | 4Q 14 | 1Q 16        | 1Q 17        | 3Q 19        | 3Q 21        | ~1Q 23       |

| Symbol Rate       | Standard Channel, Gsps (Gbps)                                | -     | 2.8 (6.4)    | 3.5 (8.0)    | 6 (13.7)     | 6 (13.7)     | ~5 (17.8)    |

| (Gsps/Lane)       | Short Channel, Gsps (Gbps)                                   | -     | 3.0 (6.9)    | 4.5 (10.3)   | 8 (18.3)     | 8 (18.3)     | ~7 (24.9)    |

|                   | Basic Pre-emphasis                                           |       | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ |

| Increased         | Advanced TxEQ, Calibration Additional UI (RCLK) Jitter specs |       |              | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ |

| Symbol Rate       | Rx Equalization                                              |       |              |              | $\checkmark$ | $\checkmark$ | $\checkmark$ |

|                   | Multi-phase 18-state coding (3.556 coding factor)            |       |              |              |              |              | $\checkmark$ |

| Dower Doduction   | Unterminated Mode                                            |       | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ |

| Power Reduction   | Reduced Amplitude "LVHS" Mode option                         |       |              | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ |

| LP Mode           | Alternate Low-Power Mode                                     |       |              | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ |

|                   | 16-bit/32-bit PPI                                            |       | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ |

|                   | 16-bit/32-bit/64-bit PPI                                     |       |              |              |              | $\checkmark$ | $\checkmark$ |

|                   | HS Reverse Mode                                              |       |              | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ |

|                   | Sync Word Selection to enhance Scrambling                    |       |              | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ |

| Enhanced Function | PHY Generated/Detected Packet Delimiter                      |       |              | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ |

| Enhanced Function | Fast Lane Turnaround                                         |       |              |              | $\checkmark$ | $\checkmark$ | $\checkmark$ |

|                   | 4m channel support, for IoT use cases                        |       |              |              | $\checkmark$ | $\checkmark$ | $\checkmark$ |

|                   | MIPI terminology update                                      |       |              |              |              | $\checkmark$ | $\checkmark$ |

|                   | Guidance for LVHS mode with CTLE.                            |       |              |              |              |              | $\checkmark$ |

|                   | Investigate: multipoint, ALP noise margin, testing update    |       |              |              |              |              | $\checkmark$ |

| Protocol          | MIPI CSI-2 <sup>®</sup>                                      | v1.3  | -            | v2.0,2.1     | v3.0         | v4.0         | TBD          |

| Specs             | MIPI DSI-2 <sup>™</sup>                                      | -     | v1.0         | v1.1         | -            | v2.0         | TBD          |

MOBILE & BEYOND

#### MIPI.ORG/DEVCON

#### mipi **DEVCON**

### **C-PHY v3.0 Preview**

2022

- Timeline: anticipated WG completion ~1Q 2023

- v3.0 spec development is the primary task in the C-PHY WG

- Increased coding factor enabled by 18-state coding

- Higher coding efficiency, more bits-per-symbol, coding for reduced RX jitter

- Simulations show lower emissions with 18-state coding

- New coding, mapping, calibration, new special code words, eye diagram

- Compatibility with prior C-PHY versions

- 6-state mode and LP signaling are still supported, 18-state mode is optional

- Improved margins for ALP mode

- Multipoint support for camera

- Guidance for LVHS reduced-level mode with CTLE

- Enhancements to existing Built-in Test capability

- Interconnect design guidelines app note, a companion document to v3.0

#### MIPI.ORG/DEVCON

#### MOBILE & BEYOND

#### **DEVCON** MIPI ALLIANCE DEVELOPERS CONFERENCE

#### Kirill Dimitrov Western Digital

## **MIPI M-PHY<sup>®</sup> Status/Future plans**

MIPI.ORG/DEVCON

MOBILE & BEYOND

20-21

SEPTEMBER

### **M-PHY introduction**

#### What is M-PHY?

2022

- Is a versatile physical layer targeting applications with a particular need for high data rates, low pin counts, lane scalability and power efficiency

- M-PHY is the base physical layer of JEDEC UFS 2.0, 3.0 and new 4.0.

- Poised to be dominant Mobile Storage interface deployed in 5G-enabled Smartphones

- Why M-PHY was created

- To meet the constant demand for efficient high-speed communications in mobile ecosystem

- What M-PHY is used for

- Flash memory storage and chip to chip communication applications for mobile/mobile influenced and automotive ecosystems

### **M-PHY Key features**

- Fifth generation mobile physical layer

- High performance with peak transmission rate of 23.32Gbps per lane (M-PHY v5.0)

- Low power, low latency efficient architecture, excellent for battery powered, mobile and mobile influenced systems.

- Low EMI

2022

- Optimized for advanced storage

- Extensive debug features

#### **M-PHY Feature Roadmap**

| Category          | Feature                                                 | v2.0         | v3.1         | v4.1         | v5.0         | v6.0         |

|-------------------|---------------------------------------------------------|--------------|--------------|--------------|--------------|--------------|

|                   | Board Adoption                                          | Q2 12        | Q2 14        | Q1 17        | ~Q4 21       | ~2025        |

| Data rate         | Max data rate per lane (Rate B Gbps)                    | ~3           | ~6           | ~12          | ~24          | TBD          |

|                   | Mobile Long Channel (CH2, channel length in inches)     | ~13          | ~13          | ~13          | -            | -            |

| Channel support   | Mobile Standard Channel (CH1, channel length in inches) | ~6           | ~6           | ~6           | ~6           | ~6           |

|                   | Automotive Channel                                      |              |              |              |              | TBD          |

|                   | Tx De-emphasis                                          |              | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ |

| Equalization      | Rx Equalization                                         |              |              | $\checkmark$ | $\checkmark$ | $\checkmark$ |

|                   | Advanced Tx and RX equalization                         |              |              |              |              | $\checkmark$ |

| Power Reduction   | Unterminated Mode                                       | $\checkmark$ | $\checkmark$ | $\checkmark$ | -            | -            |

| Power Reduction   | Burst mode transmission                                 | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ |

| LP Mode           | H8 using SQ operation                                   | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ |

|                   | High speed start up                                     |              |              |              | $\checkmark$ | $\checkmark$ |

|                   | Low speed start up                                      | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | -            |

|                   | Low speed signaling                                     | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | -            |

|                   | Eye monitor                                             |              |              |              | $\checkmark$ | $\checkmark$ |

|                   | Shared reference clock only                             |              |              |              | $\checkmark$ | $\checkmark$ |

| Enhanced Function | PAM4 or shorter channel NRZ (need feasibility)          |              |              |              |              | TBD          |

|                   | Timing parameters updates                               |              | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ |

|                   | Advanced training                                       |              |              |              |              | TBD          |

|                   | FEC or other error correction (if PAM4 will be chosen)  |              |              |              |              | TBD          |

|                   | Data-rate adjustments for integer PLL                   |              |              |              | $\checkmark$ | $\checkmark$ |

|                   | Frequency Offset PPM differences minimized              |              |              |              | $\checkmark$ | $\checkmark$ |

| Protocol          | MIPI UniPro®                                            | v1.4         | v1.6         | v1.8         | v2.0         | v3.0         |

| Specs             | UFS                                                     | v1.0         | v2.0         | v3.0/3.1     | v4.0         | v5.0         |

MOBILE & BEYOND

#### MIPI.ORG/DEVCON

### **M-PHY Future plans**

- What is next for M-PHY

- M-PHY six's generation development is about to start

- Targeting bandwidth increase and throughput enhancement

MOBILE & BEYOND

- Penetrating new ecosystems and utilizing new use cases

- Backward compatibility is a key pathway

2022

### mipi<sup>®</sup> DEVCON

MIPI.ORG/DEVCON

MIPI ALLIANCE DEVELOPERS CONFERENCE

# THANK YOU!

MOBILE & BEYOND

20-21

SEPTEMBER

()

#### ADDITIONAL RESOURCES

2022

- MIPI A-PHY, learn more:

- <u>https://www.mipi.org/specifications/a-phy</u>

- MIPI C-PHY, learn more:

- <u>https://www.mipi.org/specifications/c-phy</u>

- MIPI D-PHY, learn more:

- <u>https://www.mipi.org/specifications/d-phy</u>

- MIPI M-PHY, learn more:

- <u>https://www.mipi.org/specifications/m-phy</u>

### mipi<sup>®</sup> DEVCON

MIPI ALLIANCE DEVELOPERS CONFERENCE

## 20-21 september 2022

MIPI.ORG/DEVCON

M@BILE & BEY@ND