# mipi<sup>®</sup> DEVCON

Thierry Berdah, Yafit Snir Cadence Design Systems

Next Generation Verification Process for Automotive and Mobile Designs with MIPI CSI-2<sup>SM</sup> Interface MIPI ALLIANCE DEVELOPERS CONFERENCE

SEOUL

## Agenda

- Typical Verification Challenges of MIPI CSI-2<sup>SM</sup> designs

- IP, Sub System and System Level Verification

- Simulation verification methodology for MIPI CSI-2<sup>SM</sup> spec compliancy

- Acceleration Methodology Overview

- Concepts for building MIPI CSI-2<sup>SM</sup> acceleration-ready environment

- MIPI CSI-2<sup>SM</sup> IP Level: From simulation to acceleration

**Cadence Design Systems**

### **MIPI CSI-2<sup>sm</sup> adoption**

- Widely adopted serial high-speed protocols

- Implemented in complex systems, for a variety of applications in different markets:

- Mobile

- Video Games

- Automotive

- Multimedia

- Virtual reality, augmented reality and others

MIPI ALLIANCE DEVELOPERS CONFERENCE 19 OCTOBER 2018 SEOUL

**Cadence Design Systems**

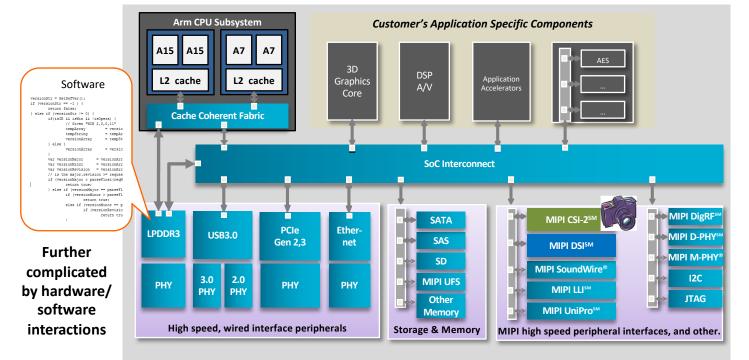

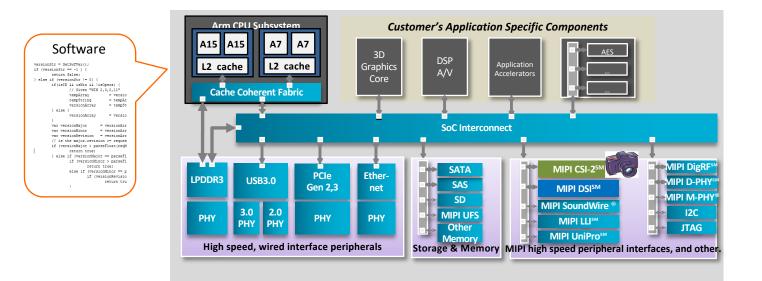

## **MIPI Interfaces usage example in Complex SOCs**

#### **Cadence Design Systems**

#### MIPI.ORG/DEVCON | 2018

MIPI ALLIANCE DEVELOPERS CONFERENCE

SEOUL

# **MIPI CSI-2<sup>SM</sup> Verification Challenges**

- Reach system verification coverage goals prior to code freeze

- MIPI CSI-2<sup>SM</sup> spec compliancy based on design and system configuration

- Time to market: Requires parallel development of hardware and software design, early in development cycle

- Validating software and hardware integration

- Create and validate real world scenarios in a pre-silicon environment

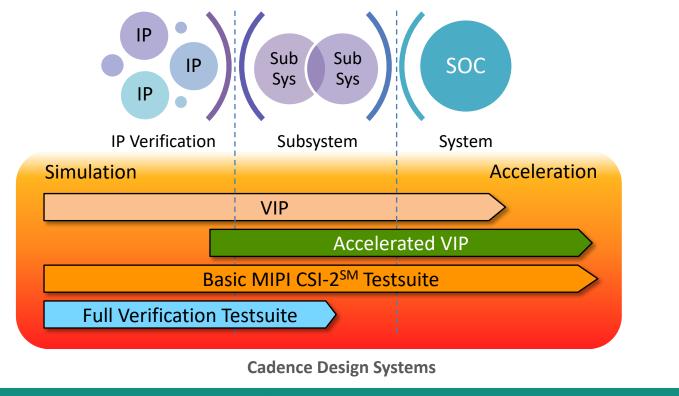

### **Design Verification Flow**

MIPI.ORG/DEVCON | 2018

ONFEDEN

19 OCTOBER 2018

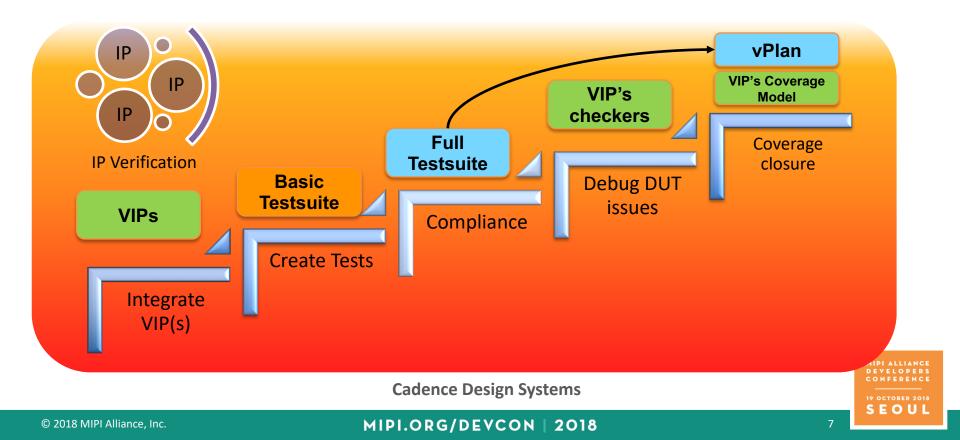

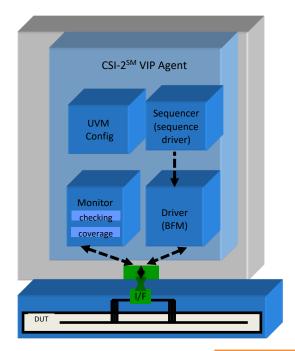

### **IP-Level Verification**

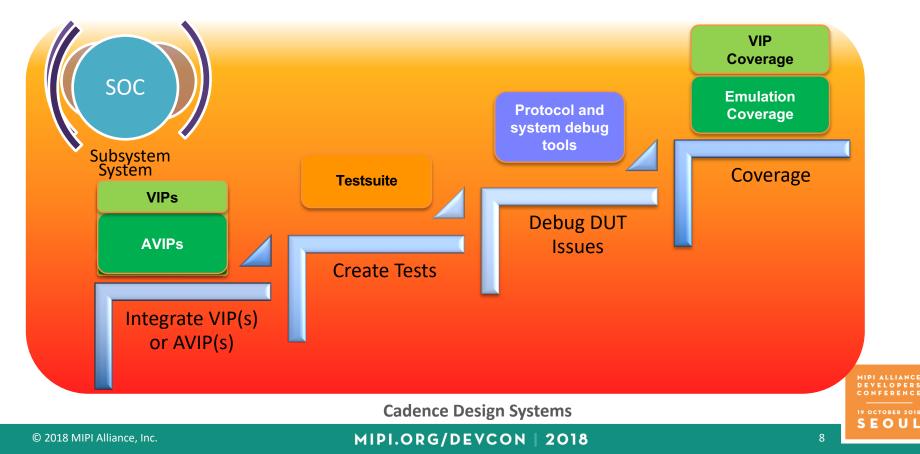

## Sub-System/SoC Level Verification

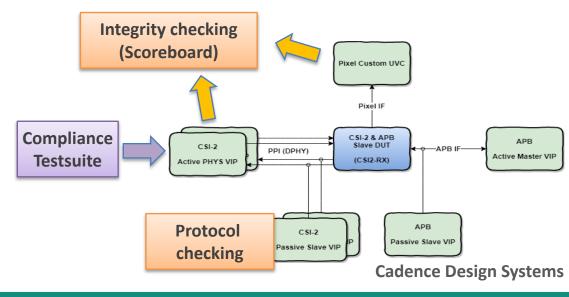

- Spec verification is based on two aspects:

- 1. MIPI CSI-2<sup>SM</sup> I/F spec compliance

- Protocol checking based on MIPI CSI-2<sup>SM</sup> spec

- Coverage aligned to the design configuration

- Complete Testsuite to cover MIPI CSI-2<sup>SM</sup> DUT

- 2. System behavioral correctness

- Integrity checking based on system definition

#### **Cadence Design Systems**

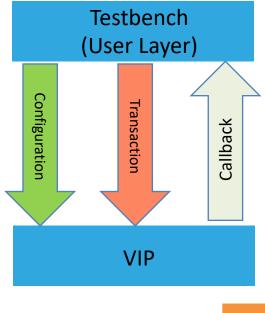

User needs full visibility into and controllability over VIP on Configuration, traffic injection, protocol checking and functional coverage

#### © 2018 MIPI Alliance, Inc.

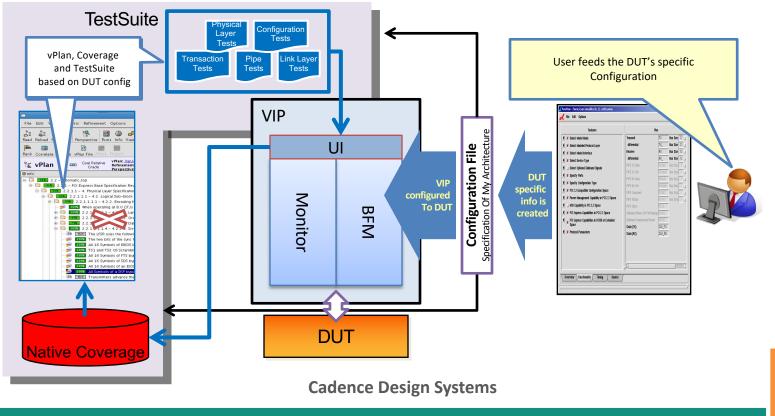

#### 1. Test Suite

- Ready to use, spec driven tests

- Optimized combination of Directed and Constrained-random sequences

- Reaching 100% of the Verification Plan

- Filtered per DUT configuration

- Early & Fast verification

#### 2. VIP Functional Coverage

- Native verification language database

- Reachable and tested

- Filtered per user configuration

- Complete coverage of <u>your</u> configuration

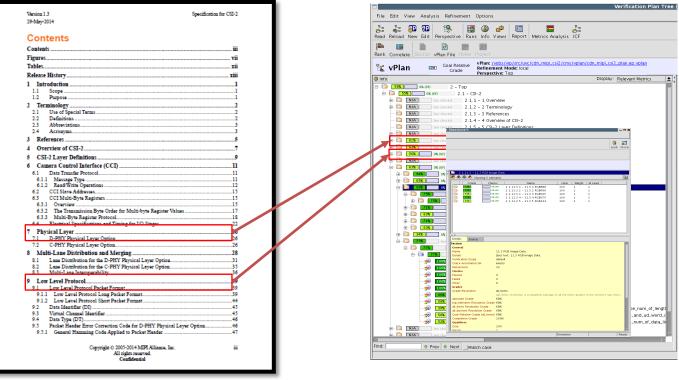

#### 3. Verification Plan

- Protocol-meaningful verification objectives

- Linked to coverage database

- Filtered to match DUT specific configuration

- Able to integrate with simulation tools

- Easy to understand correlation of coverage results to protocol specification

MIPI ALLIANCE DEVELOPERS CONFERENCE

19 OCTOBER 2018 SEOUL

# **Full** Verification

#### **Cadence Design Systems**

MIPI.ORG/DEVCON | 2018

MIPI ALLIANCE DEVELOPERS CONFERENCE

19 OCTOBER 2018

# How to create the MIPI CSI-2<sup>SM</sup> Verification Plan?

#### **Cadence Design Systems**

#### MIPI.ORG/DEVCON | 2018

MIPI ALLIANCE

19 OCTOBER 2018

mipi **DEV**CON

## **Development Flow and VIP Tools Map**

# Why Acceleration ?

Complex SoCs, comprised of tens of millions of logic gates, will impede software simulators, even when running on the fastest servers.

**Cadence Design Systems**

MIPI.ORG/DEVCON | 2018

CONFERENCE

SEOUL

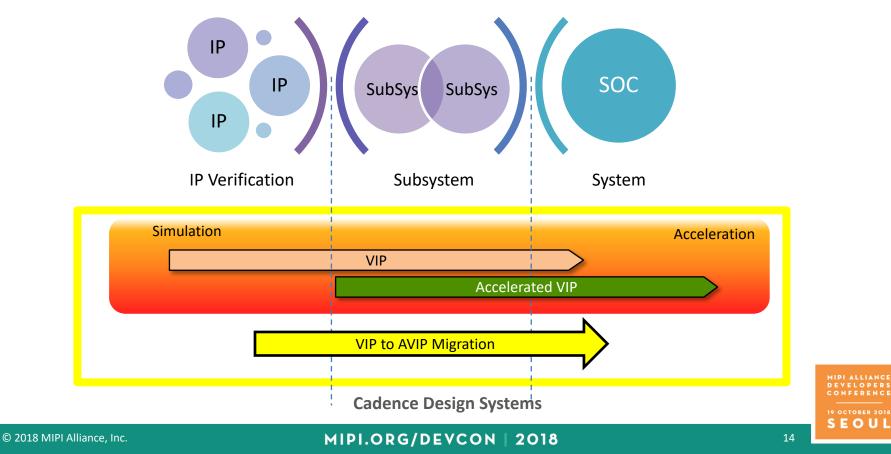

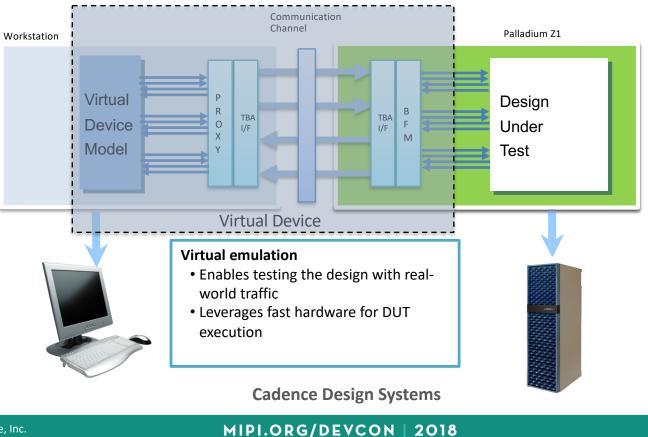

# **Overview of hardware assisted verification**

- Emulator assisted verification

- Simulation Acceleration

- Virtual Emulation

- In-Circuit Emulation

FPGA Prototyping

**Cadence Design Systems**

MIPI.ORG/DEVCON | 2018

MIPI ALLIANCE DEVELOPERS CONFERENCE 19 OCTOBER 2018 SEOUL

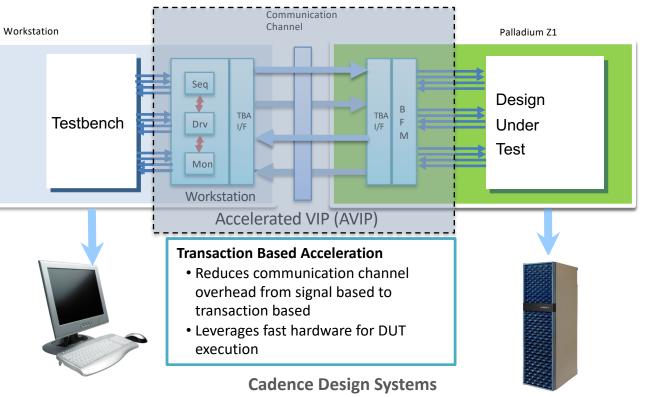

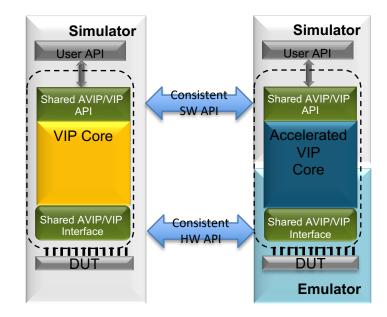

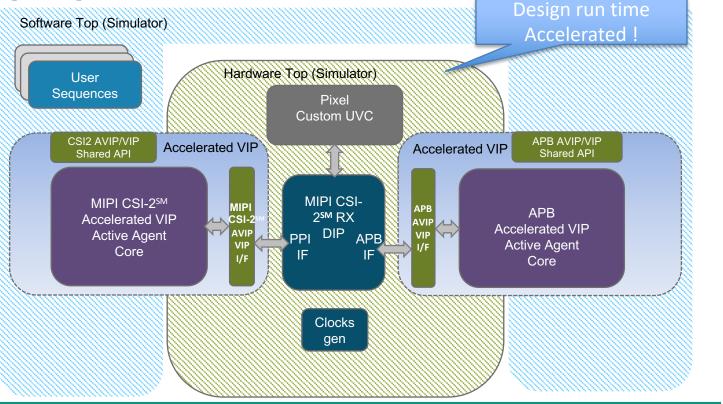

### **Simulation Acceleration & Accelerated VIP**

#### **Transaction Based Acceleration**

MIPI ALLIANCE DEVELOPERS CONFERENCE 19 OCTOBER 2018 SEOUL

### **Virtual emulation & Virtual Device**

MIPI ALLIANCE DEVELOPERS CONFERENCE 19 OCTOBER 2018 SEOUL

#### © 2018 MIPI Alliance, Inc.

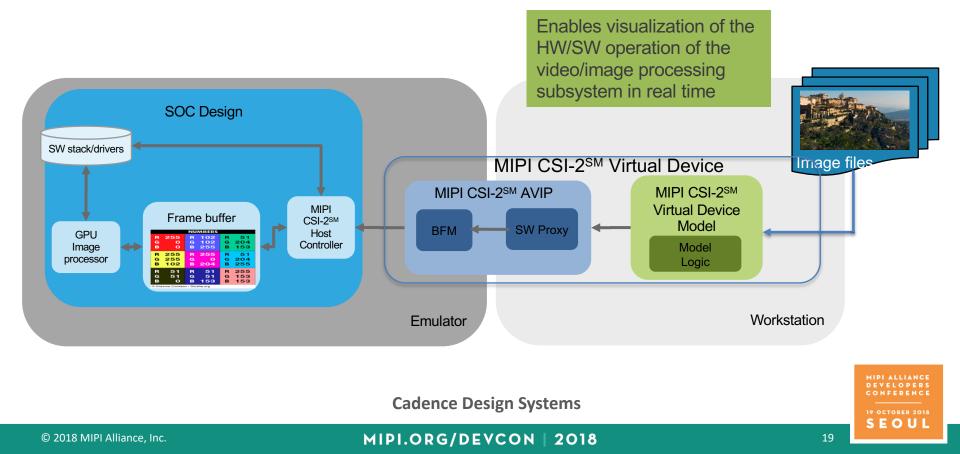

# **MIPI CSI-2<sup>SM</sup> Virtual Device**

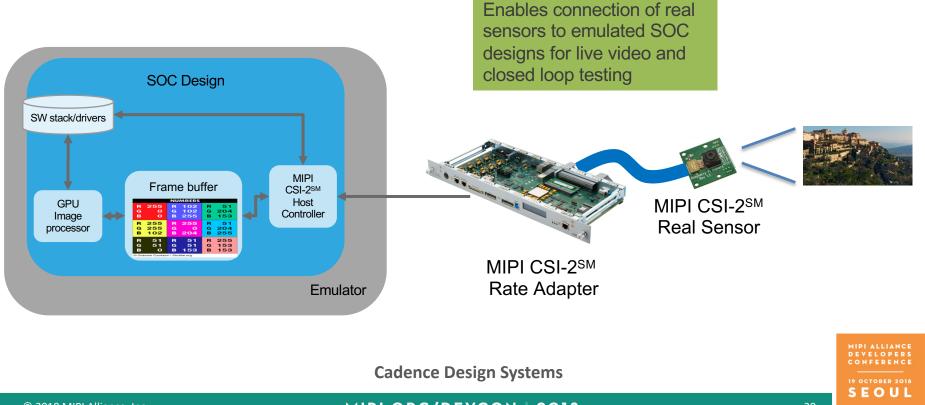

# **MIPI CSI-2<sup>SM</sup> Emulation/Prototyping with real sensor**

© 2018 MIPI Alliance, Inc.

MIPI.ORG/DEVCON | 2018

mipi **DEVCON**

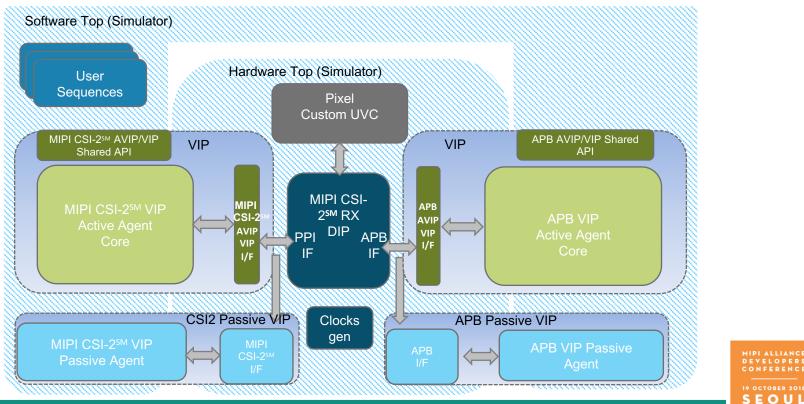

### **Concepts for building an acceleration-ready environment**

- Use consistent API for VIPs/AVIPs

- Use Dual-Top structure for the verification environment

- The Hardware top will include the DUT, Interfaces, clocks generation, etc.

- The software top will include the SW Verification Environment.

- Use event based delays instead of cycle/time based delays whenever possible.

- Pre define simulation and acceleration subset of shared sequences

**Cadence Design Systems**

#### Simulation stage

© 2018 MIPI Alliance, Inc.

MIPI.ORG/DEVCON 2018

MIPI ALLIANCE DEVELOPERS

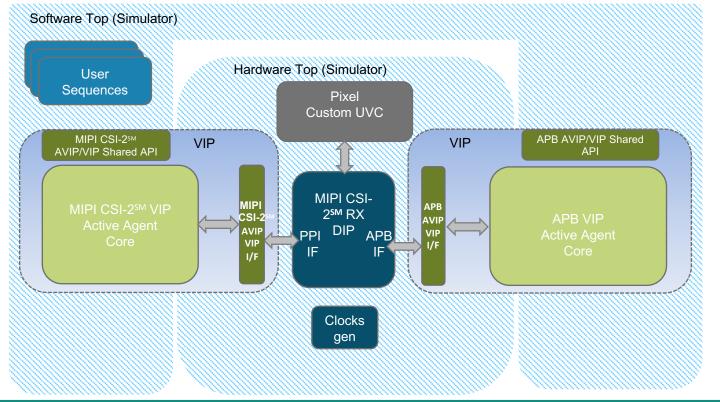

#### Step #1 Disabling passive agents used at IP level stage

© 2018 MIPI Alliance, Inc.

MIPI.ORG/DEVCON | 2018

MIPI ALLIANCE

19 OCTOBER 2018

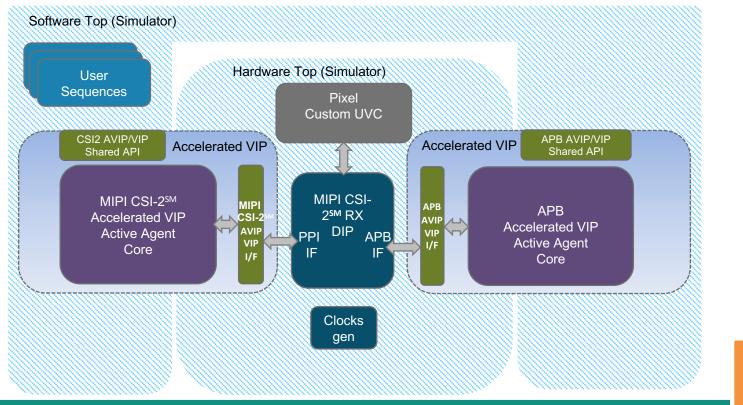

#### **Step #2 Migrating to Accelerated VIPs**

© 2018 MIPI Alliance, Inc.

MIPI.ORG/DEVCON | 2018

MIPI ALLIANC

19 OCTOBER 2018

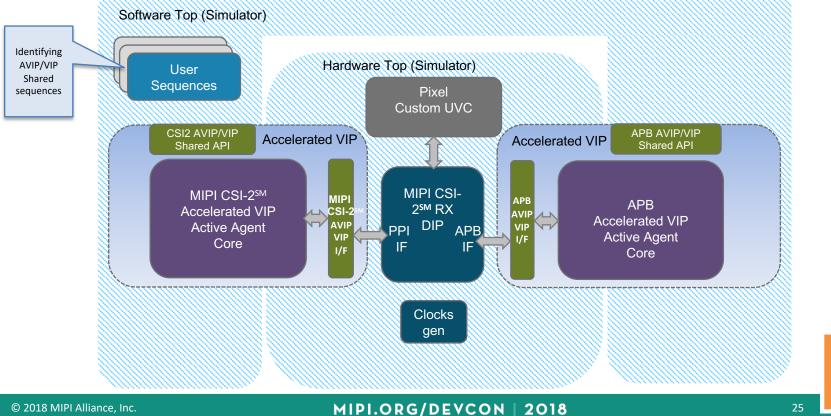

#### **Step #3 Choosing the subset of sequences required for acceleration**

© 2018 MIPI Alliance, Inc.

MIPI ALLIANC

**19 OCTOBER 2018** SEOUL

#### **Step #4 Migrating to acceleration flow**

MIPI.ORG/DEVCON | 2018

© 2018 MIPI Alliance, Inc.

26

MIPI ALLIANCE

19 OCTOBER 2018

# **Summary: Advantages of using acceleration**

- Enables orders-of-magnitude gains in throughput over Simulation

- Enables re using selected parts of your simulation verification environment

- Enables advanced technologies with virtual emulation, like:

- Hybrid operation for optimal partition of the design between HW and SW to achieve maximum speedup

- Connection to Virtual Devices, Virtual machines, etc.

- Enables OS-level benchmarks and driver bring-up

### ADDITIONAL RESOURCES

- MIPI Camera WG URL: <u>https://members.mipi.org/wg/camera-wg/dashboard</u>

- MIPI CSI-2<sup>SM</sup> Spec URL: <u>https://members.mipi.org/wg/camera-</u> wg/document/75006

- Cadence Verification IP URL: <u>https://ip.cadence.com/ipportfolio/verification-ip/simulation-vip</u>

- Cadence Accelerated VIP URL: <u>https://ip.cadence.com/ipportfolio/verification-ip/accelerated-vip</u>

# mipi DEVCON THANK YOU

#### MIPI ALLIANCE DEVELOPERS CONFERENCE

SEOUL