# mipi<sup>®</sup> DEVCON

Gordon Getty Juhyun Yang Teledyne LeCroy

Troubleshooting MIPI M-PHY<sup>®</sup> Link and Protocol Issues MIPI ALLIANCE DEVELOPERS CONFERENCE

SEOUL

# **Objective**

This presentation is intended to help MIPI UniPro<sup>®</sup>/UFS developers to find the root cause of problems more quickly by providing tips for debugging MIPI M-PHY<sup>®</sup> based devices.

### Welcome in Korean

MIPI ALLIANCE DEVELOPERS CONFERENCE 19 OCTOBER 2018 SEOUL

# mipi<sup>®</sup> DEVCON

## **MIPI Technologies**

MIPI ALLIANCE DEVELOPERS CONFERENCE

SEOUL

# **Physical Layer Interconnects**

- High Speed Interconnects

- MIPI M-PHY®

- MIPI UniPro<sup>®</sup>/UniPort

- Camera (Unipro), Storage (UniPro), Modem, Interchip

- IVIIPI D-PHY(SIVI)

- MIPI C-PHY<sup>(SM)</sup>

- Camera, Display

- MIPI A-PHY<sup>(SM)</sup>

- Automotive applications

- Low Speed Interconnects

- SLIMBus®

- Audio

- SoundWire<sup>®</sup>

- Audio

- CMOS I/O

- Chip to Chip

# mipi<sup>®</sup> DEVCON

### **MIPI M-PHY®**

MIPI ALLIANCE DEVELOPERS CONFERENCE

SEOUL

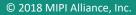

## **MIPI M-PHY® Protocols**

- M-PHY<sup>®</sup> protocols are used based on interface used in each application.

- Multiple protocols can be used in a single device.

# Why MIPI M-PHY<sup>®</sup>?

From the MIPI M-PHY<sup>®</sup> Specification V4.0:

"Mobile devices face increasing bandwidth demands for each of its functions as well as an increase of the number of functions integrated into the system. This requires wide bandwidth, low-pin count (serial) and highly power-efficient (network) interfaces that provides sufficient flexibility to be attractive for multiple applications, but which can also be covered with one physical layer technology. MIPI M-PHY<sup>®</sup> is the successor of MIPI D-PHY<sup>(SM)</sup>, requiring less pins and providing more bandwidth per pin (pair) with improved power efficiency."

## **MIPI M-PHY® Data Rates**

- LS-MODE

- Gears 0-7

- HS-MODE

- Gears 1-4

- All Modules (Host and Device) must support LS

- Default for PWM is Gear1 3-9Mbs

- Each Gear supports 2x higher speeds

- one GEAR below the default speed range (PWM-G0)

- HS-Mode is Optional

- HS-MODE includes a default GEAR (HS-G1)

- Optional High Speed GEARs (HS-G2, HS-G3, HS-G4) at incremental 2x higher rates

- Each GEAR includes two data rates for EMI mitigation reasons

- E.g. HS-G1 supports 1.25 Gbps and 1.45 Gbps

- These two data rates are known as A & B

- Support for a LS or a HS GEAR requires support for all GEARs below

MIPI ALLIANCE DEVELOPERS CONFERENCE 19 OCTOBER 2018 **SEOUL**

## MIPI M-PHY<sup>®</sup> HS Gear 4

• Doubling of the Data Rate from HS-Gear3 to HS-Gear4

| RATE A-series (Mbps) | RATE B-series <sup>1</sup> (Mbps) | High-Speed GEARs |

|----------------------|-----------------------------------|------------------|

| 1248                 | 1457.6                            | HS-G1 (A/B)      |

| 2496                 | 2915.2                            | HS-G2 (A/B)      |

| 4992                 | 5830.4                            | HS-G3 (A/B)      |

| 9984                 | 11660.8                           | HS-G4 (A/B)      |

### Table 11 HS-BURST: RATE Series and GEARs

The B-series rates shown are not integer multiples of common reference frequencies 19.20 MHz or 26.00 MHz, but are within the tolerance range of 2000 ppm.

# mipi<sup>®</sup> DEVCON

### **MIPI UniPro®**

MIPI ALLIANCE DEVELOPERS CONFERENCE

SEOUL

# MIPI UniPro®

- MIPI specification to the define protoc between Devices that implement the

- This includes definitions of data struct Frames, used to convey information a

- Flow control, error handling, power ar connection services are also defined in

- UniPro version 1.61, the use of M-PHY chip interconnections

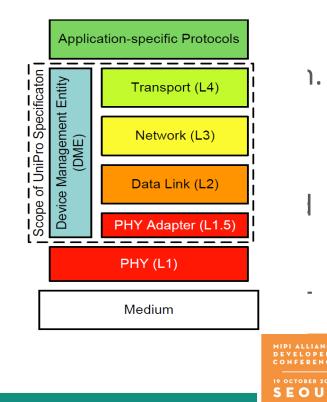

## MIPI UniPro<sup>®</sup> L1.5 Protocol

- The L1.5 for MIPI M-PHY<sup>®</sup> automates a significant part of the required steps used for Power Modes control, utilizing an L1.5-to-L1.5 communication protocol known as PACP (PHY Adapter Control Protocol).

- PDUs ("PACP frames") generated by L1.5 are multiplexed with the symbol stream received from L2 and can be recognized by a unique header pattern.

## MIPI UniPro<sup>®</sup> L1.5 Power States and Power Modes

- The difference between Power States and Power Modes are as follows:

- An Application can set only a Power Mode, but cannot set a Power State

- An Application can get a Power Mode and get a Power State

- the gettable value of a Power Mode simply reflects the value that was set

- the gettable value of a Power State may change spontaneously when in FastAuto\_Mode or SlowAuto\_Mode

### **MIPI UniPro® PACP Capability Exchange**

| 832 | Sublink0 | 5.111370 | PACP_CAP_EXT1_ind |                   | PWM-G1 x1 |

|-----|----------|----------|-------------------|-------------------|-----------|

| 833 | Sublink0 | 5.111398 | PACP_CAP_ind      |                   | PWM-G1 x1 |

| 840 | Sublink1 | 5.111968 |                   | PACP_CAP_EXT1_ind | PWM-G1 x1 |

| 842 | Sublink1 | 5.112047 |                   | PACP_CAP_ind      | PWM-G1 x1 |

| 0  | ESC_PA              | EscPa           | rm_PA            |  |  |  |  |  |

|----|---------------------|-----------------|------------------|--|--|--|--|--|

|    | MK1                 |                 | 01               |  |  |  |  |  |

| 2  | PAG                 | CP_FunctionId   |                  |  |  |  |  |  |

|    |                     | 0x0309          |                  |  |  |  |  |  |

| 4  | THibern8            | TMinActivate    | Status           |  |  |  |  |  |

|    | 0x01                | 0x6             | 0xF              |  |  |  |  |  |

| 6  | TAdvHibern8         | TAdvMinActivate | RxAdvGranularity |  |  |  |  |  |

|    | 0x01                | 0xA             | 0x4              |  |  |  |  |  |

| 8  | MinRxTrailingClocks | RxPwmBurst      | ClosureLength    |  |  |  |  |  |

|    | 0x2E                | O               | 0x1F             |  |  |  |  |  |

| 10 | RxLsPrepareLength   | RxPwmG6G        | 7SyncLength      |  |  |  |  |  |

|    | 0x0D                | 0×              | (00              |  |  |  |  |  |

| 12 | RxHsG1PrepareLength | RxHsG1S         | yncLength        |  |  |  |  |  |

|    | OxOF                | 0×              | 48               |  |  |  |  |  |

| 14 | RxHsG2PrepareLength | RxHsG2S         | yncLength        |  |  |  |  |  |

|    | 0x0F                | O               | 49               |  |  |  |  |  |

| 16 | RxHsG3PrepareLength | RxHsG3S         | yncLength        |  |  |  |  |  |

|    | OxOF                | 0x              | 4A               |  |  |  |  |  |

| 18 | Res                 | served [31:16]  |                  |  |  |  |  |  |

|    |                     | Oxffff          |                  |  |  |  |  |  |

| 20 | Re                  | served [15:0]   |                  |  |  |  |  |  |

|    |                     | Oxffff          |                  |  |  |  |  |  |

| 22 | C                   | CITT CRC-16     |                  |  |  |  |  |  |

|    |                     | 0xDB44          |                  |  |  |  |  |  |

MIPI ALLIANCE DEVELOPERS CONFERENCE 19 OCTOBER 2018 SEOUL

© 2018 MIPI Alliance, Inc.

### MIPI UniPro<sup>®</sup> Layer 1.5 Example – PACP\_PWR\_REQ

### Used for power mode changes

| FRAME 696 | 3.947_976_272 s | 0.000_203_592 s  | LS              | 1             | 0          | PACP      | PACP_PWR_REQ       |      |              |  |  |  |

|-----------|-----------------|------------------|-----------------|---------------|------------|-----------|--------------------|------|--------------|--|--|--|

| FRAME 706 | 3.948_213_046 s | 0.000_219_178 s  | LS              | 1             | 0          |           |                    | PACP | PACP_PWR_CNF |  |  |  |

|           |                 |                  | 0x01            |               |            |           |                    |      |              |  |  |  |

|           | PACP_FunctionId |                  | 0x010E : PAC    | P_PWR_        | REQ        |           |                    |      |              |  |  |  |

|           | DevId           |                  | 0x00            |               |            |           |                    |      |              |  |  |  |

| ~         | Flags           |                  | 0x36            | 0x36          |            |           |                    |      |              |  |  |  |

|           | Scrambling re   | quest            | 0x0 : Not req   | uested        |            |           |                    |      |              |  |  |  |

|           | UserDataVali    | d                | 0x1:Valid       |               |            |           |                    |      |              |  |  |  |

|           | HS Series       |                  | 0x1 : Series B  | }             |            |           |                    |      |              |  |  |  |

|           | LINE-RESET I    | 0x0 : Not req    | uested          |               |            |           |                    |      |              |  |  |  |

|           | PA_TxTermin     | ation            | 0x1:Enable      |               |            |           |                    |      |              |  |  |  |

|           | PA_RxTermin     | PA_RxTermination |                 |               | 0x1:Enable |           |                    |      |              |  |  |  |

|           | - TxMode        |                  | 0x1 : Fast_Mode |               |            |           |                    |      |              |  |  |  |

|           | TxLane          |                  | 0x1:1Lane       |               |            |           |                    |      |              |  |  |  |

|           | TxGear          |                  | 0x1             |               |            |           |                    |      |              |  |  |  |

|           | RxMode          |                  | 0x1:Fast_M      | 0x1:Fast_Mode |            |           |                    |      |              |  |  |  |

|           | RxLane          |                  | 0x1:1Lane       |               |            |           |                    |      |              |  |  |  |

| -         | RxGear          |                  | 0x1             |               |            |           |                    |      |              |  |  |  |

|           | - PAPowerModeUs | erData           | 0x00000000      | 0000000       | 00000      | 000 FFFFF | FFF FFFFFFFF FFFFF | FFF  |              |  |  |  |

|           | - CRC-16        |                  | 0x7A4E          |               |            |           |                    |      |              |  |  |  |

MIPI ALLIANCE DEVELOPERS CONFERENCE 19 OCTOBER 2018 **SEOUL**

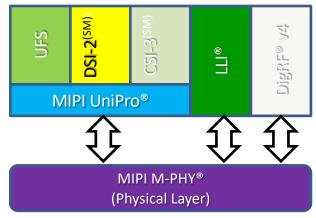

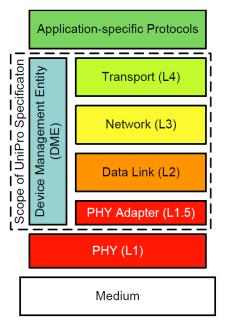

# MIPI UniPro<sup>®</sup> Layers

- L2 The Data Link Layer provides reliable Links between a transmitter and a directly attached receiver

- L3 Network Layer is to allow data to be routed to the proper destination in a networked environment.

- L4 Transport Layer mechanisms allow a single physical Packet stream between two Devices to support multiple, independent, logical Packet streams or "Connections".

|          | Appli                                                             | cation-specific Protocols |

|----------|-------------------------------------------------------------------|---------------------------|

| ficaton  | Scope of UniPro Specificaton<br>Device Management Entity<br>(DME) | Transport (L4)            |

| ro Speci |                                                                   | Network (L3)              |

|          |                                                                   | Data Link (L2)            |

| Scop     |                                                                   | PHY Adapter (L1.5)        |

|          |                                                                   | PHY (L1)                  |

|          |                                                                   | Medium                    |

E O U

# mipi<sup>®</sup> DEVCON

### Universal Flash Storage (UFS) JEDEC

MIPI ALLIANCE DEVELOPERS CONFERENCE

SEOUL

## **UFS – Universal Flash Storage**

- Universal Flash Storage JEDEC Standard JESD220B

- Universal Flash Storage (UFS) is a simple, high performance, mass storage device with a serial interface.

- It is primarily used in mobile systems, between host processing and mass storage memory devices.

- MIPI M-PHY<sup>®</sup> and MIPI UniPro<sup>®</sup> make up the interconnect for UFS

- UFS is architected on SCSI SAM

- UFS uses the command layers from SCSI SPC and SBC

| Universal Flash Storage (UFS)<br>Version 2.0<br>JESD220B<br>(Privates of JESD220A, June 2012)<br>SEPTEMBER 2013 | JEDEC<br>STANDARD                                        |  |

|-----------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|--|

| (Bernise of RED220A, June 2012)<br>SEPTEMBER 2013                                                               |                                                          |  |

|                                                                                                                 |                                                          |  |

|                                                                                                                 | EPTEMBER 2013<br>EDEC SOLID STATE TECHNOLOGY ASSOCIATION |  |

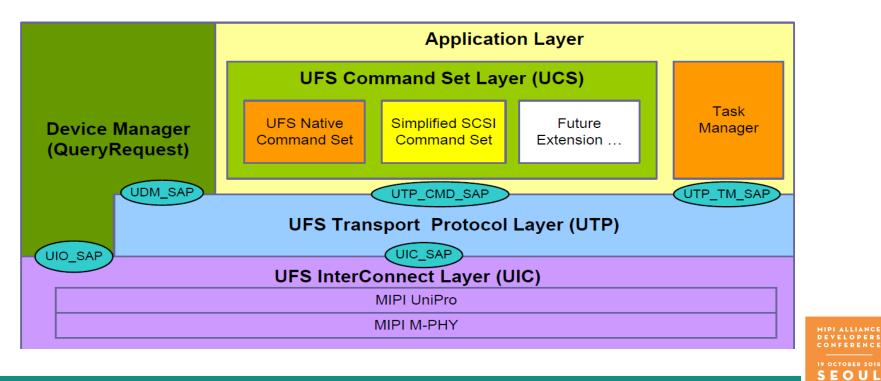

### **UFS Architecture**

© 2018 MIPI Alliance, Inc.

## **UFS Physical Layer Requirements**

- UFS interface can support multiple lanes.

- Each lane consists of a differential pair.

- Basic configuration is based on one transmit lane and one receive lane.

- Optionally, a UFS device may support two downstream lanes and two upstream lanes. An equal number of downstream and upstream lanes shall be provided in each link.

- Links must be symmetrical

21

## **Application Specific Protocol - UFS**

- The application layer consists of the UFS Command Set layer (UCS), the device manager and the Task Manager

- The UCS will handle the normal commands like read, write, and so on.

- UFS may support multiple command sets.

- UFS is designed to be protocol agnostic. This version UFS standard uses SCSI as the baseline protocol layer.

- A simplified SCSI command set was selected for UFS.

- UFS Native command set can be supported when it is needed to extend the UFS functionalities.

- The Task Manager handles commands meant for command queue control.

- The Device Manager will provide device level control like Query Request and lower level link-layer control.

| In test | Index | Direction | Time     | Host0                           | Device1                          | Power Mode |

|---------|-------|-----------|----------|---------------------------------|----------------------------------|------------|

|         | 4     | Sublink0  | 16.65201 | QUERY REQUEST (READ FLAG)       |                                  | PWM-G1 x1  |

|         | 5     | Sublink1  | 16.65222 |                                 | QUERY RESPONSE (READ FLAG)       | PWM-G1 x1  |

|         | 6     | Sublink0  | 16.70338 | QUERY REQUEST (READ FLAG)       |                                  | PWM-G1 x1  |

|         | 7     | Sublink1  | 16.70358 |                                 | QUERY RESPONSE (READ FLAG)       | PWM-G1 x1  |

|         | 8     | Sublink0  | 16.70470 | REQUEST SENSE                   |                                  | PWM-G1 x1  |

|         | 9     | Sublink1  | 16.70490 |                                 | REQUEST SENSE RESPONSE (DATA IN) | PWM-G1 x1  |

|         | 10    | Sublink1  | 16.70498 |                                 | RESPONSE                         | PWM-G1 x1  |

|         | 11    | Sublink0  | 16.70643 | REQUEST SENSE                   |                                  | PWM-G1 x1  |

|         | 12    | Sublink1  | 16.70663 |                                 | REQUEST SENSE RESPONSE (DATA IN) | PWM-G1 x1  |

|         | 13    | Sublink1  | 16.70672 |                                 | RESPONSE                         | PWM-G1 x1  |

|         | 14    | Sublink0  | 16.91731 | QUERY REQUEST (WRITE ATTRIBUTE) |                                  | PWM-G1 x1  |

|         | 15    | Sublink1  | 16.91779 |                                 | QUERY RESPONSE (WRITE ATTRIBUTE) | PWM-G1 x1  |

|         | 16    | Sublink0  | 17.64016 | WRITE (16)                      |                                  | HS-G3B x1  |

|         | 17    | Sublink1  | 17.64021 |                                 | READY TO TRANSFER                | HS-G3B x1  |

|         | 18    | Sublink0  | 17.64022 | WRITE (16) DATA (DATA OUT)      |                                  | HS-G3B x1  |

|         | 19    | Sublink1  | 17.64049 |                                 | RESPONSE                         | HS-G3B x1  |

|         | 20    | Sublink0  | 17.64089 | READ (16)                       |                                  | HS-G3B x1  |

|         | 21    | Sublink1  | 17.64095 |                                 | READ (16) DATA (DATA IN)         | HS-G3B x1  |

|         | 22    | Sublink1  | 17.64107 |                                 | RESPONSE                         | HS-G3B x1  |

|         | 23    | Sublink0  | 17.64153 | WRITE (16)                      |                                  | HS-G3B x1  |

|         | 24    | Sublink1  | 17.64158 |                                 | READY TO TRANSFER                | HS-G3B x1  |

|         | 25    | Sublink0  | 17.64159 | WRITE (16) DATA (DATA OUT)      |                                  | HS-G3B x1  |

## **SCSI Read Command**

|         |       | last et l | <b>-</b> |                                 |          | Packet D   | lecode                 |                   |                        |               |       | <b>-</b> ↓ ×           |

|---------|-------|-----------|----------|---------------------------------|----------|------------|------------------------|-------------------|------------------------|---------------|-------|------------------------|

| In test | Index | Direction | Time     | Host0                           | Device1  | Packet: 20 | ), Host0, READ (16)    |                   |                        |               | 8     | 16 32                  |

|         | 4     | Sublink0  | 16.65201 | QUERY REQUEST (READ FLAG)       |          |            |                        |                   |                        |               |       |                        |

|         | 5     | Sublink1  | 16.65222 |                                 | QUERY F  | Byte       | +                      | +0                |                        | +1            |       | Î                      |

|         | 6     | Sublink0  | 16.70338 | QUERY REQUEST (READ FLAG)       |          | 0          | HD DD Transaction Code |                   | Re   R   W.            | Peropuo       |       | ATTR                   |

|         | 7     | Sublink1  | 16.70358 |                                 | QUERY F  | U          | 0x0 0x0                | 0x1               | 0x0 0x1 0x0            |               | 0x0   | 0x0                    |

|         | 8     | Sublink0  | 16.70470 | REQUEST SENSE                   |          | 2          | <u>*</u> *             | UN                |                        | Task Tag      | UNU / |                        |

|         | 9     | Sublink1  | 16.70490 |                                 | REQUES   |            | 0)                     | x00               |                        | 0x00          |       |                        |

|         | 10    | Sublink1  | 16.70498 |                                 | RESPON   | 4          | IID                    | Command Set Type  | R                      | eserved (byte | e 5)  |                        |

|         | 11    | Sublink0  | 16.70643 | REQUEST SENSE                   |          |            | 0x0                    | 0x0               | Ox00                   |               |       |                        |

|         | 12    | Sublink1  | 16.70663 |                                 | REQUES   | 6          | Reserved (byte 6)      |                   | R                      | eserved (byte | e 7)  |                        |

|         | 13    | Sublink1  | 16.70672 |                                 | RESPON   |            | 0x00                   |                   | Į                      | 0x00          |       |                        |

|         | 14    | Sublink0  | 16.91731 | QUERY REQUEST (WRITE ATTRIBUTE) |          | 8          | EHS Length<br>0x00     |                   | R                      | eserved (byte | e 9)  |                        |

|         | 15    | Sublink1  | 16.91779 |                                 | QUERY F  | 10         | <u>0</u>               |                   | l<br>cont l consth     | 0x00          |       |                        |

|         | 16    | Sublink0  | 17.64016 | WRITE (16)                      |          | 10         |                        | -                 | gment Length<br>0x0000 |               |       |                        |

|         | 17    | Sublink1  | 17.64021 |                                 | READY T  | 12         |                        | Expected Data Tra |                        | :16]          |       |                        |

|         | 18    | Sublink0  | 17.64022 | WRITE (16) DATA (DATA OUT)      |          |            |                        |                   | 0000                   |               |       |                        |

|         | 19    | Sublink1  | 17.64049 |                                 | RESPON   | 14         |                        | Expected Data Tra | nsfer Length [1        | 5:0]          |       |                        |

|         | 20    | Sublink0  | 17.64089 | READ (16)                       |          |            |                        | 0x1               | 000                    |               |       |                        |

|         | 21    | Sublink1  | 17.64095 |                                 | READ (1) | 16         |                        | ion Code          | RDPROTECT              | DPO FUA       |       |                        |

|         | 22    | Sublink1  | 17.64107 |                                 | RESPON   |            | 0                      |                   | 0x0                    | 0x0 0x0       | 0x0   | 0x0   0x0              |

|         | 23    | Sublink0  | 17.64153 | WRITE (16)                      |          | 10         |                        | HS-G3B x1         | ATTIMUECE 163.4        | 01            |       |                        |

|         | 24    | Sublink1  | 17.64158 |                                 | READY TO | D TRANS    | FER                    | HS-G3B x1         |                        |               |       | MIPI ALLIA<br>DEVELOPI |

|         | 25    | Sublink0  | 17.64159 | WRITE (16) DATA (DATA OUT)      |          |            |                        | HS-G3B x1         |                        |               |       | CONFEREN               |

### MIPI.ORG/DEVCON | 2018

SEOUL

### **SCSI Write Command**

| In test | Index | Direction | Time     | Host0                           | Device1 | Packet De                     | code      |             |          |                |                     | <b>▼</b> □ 3                 | ×   |

|---------|-------|-----------|----------|---------------------------------|---------|-------------------------------|-----------|-------------|----------|----------------|---------------------|------------------------------|-----|

|         | 0     | Sublink0  | 4.186909 | NOP OUT                         |         | Packet: 16, Host0, WRITE (16) |           |             | 8 16 32  |                | 32                  |                              |     |

|         | 1     | Sublink1  | 4.187109 |                                 | NOP IN  | Byte                          |           | +0          |          |                | +1                  |                              |     |

|         | 2     | Sublink0  | 4.188010 | QUERY REQUEST (SET FLAG)        |         | byte                          |           |             |          |                | 1                   |                              |     |

|         | 3     | Sublink1  | 4.188210 |                                 | QUERY R | 0                             | H D  1    | Transaction | Code     | R R W R        | ese  CP  /          | ATTR                         |     |

|         | 4     | Sublink0  | 4.189164 | QUERY REQUEST (READ FLAG)       |         |                               | 0 0       | 0x1         |          | 0 0 0          | 0x0 0               | 0x0                          |     |

|         | 5     | Sublink1  | 4.189364 |                                 | QUERY R | 2                             |           |             |          |                | Task Tag            |                              |     |

|         | 6     | Sublink0  | 4.240711 | QUERY REQUEST (READ FLAG)       |         | 4                             | IID       | 0x00        | mand     |                | )x00<br>ed (byte 5) |                              |     |

|         | 7     | Sublink1  | 4.240910 |                                 | QUERY R | 7                             | 0x0       |             | )x0      |                | x00                 |                              |     |

|         | 8     | Sublink0  | 4.242537 | REQUEST SENSE                   |         | 6                             | Rese      | erved (byte | 6)       | Reserve        | ed (byte 7)         |                              |     |

|         | 9     | Sublink1  | 4.242737 |                                 | REQUES  |                               |           | 0x00        |          | ÷              | )x00                |                              |     |

|         | 10    | Sublink1  | 4.242817 |                                 | RESPON  | 8                             | E         | HS Length   |          |                | ed (byte 9)         |                              |     |

|         | 11    | Sublink0  | 4.244950 | REQUEST SENSE                   |         | 10                            |           | 0x00        | ta Cana  | nent Length    | )x00                |                              |     |

|         | 12    | Sublink1  | 4.245155 |                                 | REQUES  |                               |           | Da          |          | 0000           |                     |                              |     |

|         | 13    | Sublink1  | 4.245235 |                                 | RESPON  | 12                            |           | Expected D  |          | nsfer Length [ | 31:16]              |                              |     |

|         | 14    | Sublink0  | 4.457277 | QUERY REQUEST (WRITE ATTRIBUTE) |         |                               |           | ·           | 0x0      | 0000           |                     |                              |     |

|         | 15    | Sublink1  | 4.457761 |                                 | QUERY R | 14                            | WINITE AI | Expected (  | Data Tra | ansfer Length  | [15:0]              |                              |     |

|         | 16    | Sublink0  | 5.176648 | WRITE (16)                      |         |                               |           |             | HS       | S-G3B x1       |                     | MIPI ALL<br>DEVELC<br>CONFER | OPE |

|         |       |           |          |                                 |         |                               |           |             |          |                |                     |                              |     |

19 OCTOBER 2018 SEOUL

© 2018 MIPI Alliance, Inc.

# mipi<sup>®</sup> DEVCON

## **Debugging MIPI M-PHY®**

MIPI ALLIANCE DEVELOPERS CONFERENCE

SEOUL

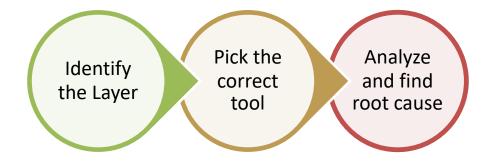

## **Debug process for Serial Protocols**

© 2018 MIPI Alliance, Inc.

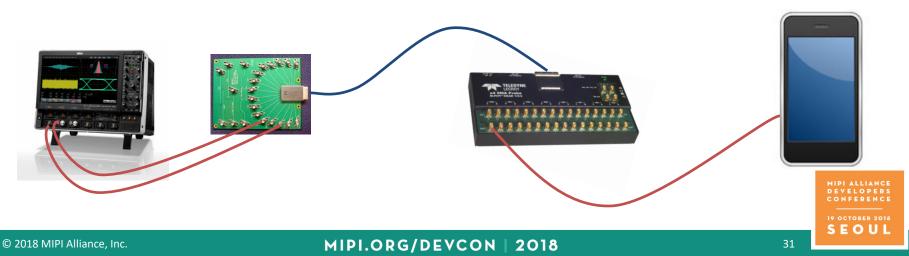

# **Debugging MIPI M-PHY®**

- Typically MIPI M-PHY<sup>®</sup> production systems are chip to chip, no connector

- Development systems may have SMA connections between devices

- First challenge is to access link

- Probing Type:

- SMA

- Multi Lead

- Midbus

- Check electrical first before debugging protocol problem

# Using the correct tool

- Is problem related to Signal Integrity?

- Are devices physically connected?

- Are both devices providing MIPI M-PHY<sup>®</sup> compliant signaling?

- Use an Oscilloscope to verify

- Is problem related to Connectivity

- Is a link established between the 2 devices?

- Is the data rate as expected?

- Can software see the devices

- for UFS, can the storage be seen?

- Use a Protocol analyzer to verify

| SCSI |      | Request Sense |

|------|------|---------------|

|      | CTRL | AFC           |

|      | UTP  | DATA IN       |

| CTRL |      | AFC           |

| CTRL |      | AFC           |

|      | UTP  | RESPONSE      |

| CTRL |      | AFC           |

| CTRL |      | AFC           |

| SCSI |      | Read (10)     |

## Which Layer is causing the problem?

- Same principle applies regardless of MIPI M-PHY<sup>®</sup> upper layer protocol

- Identify the layer

- Performance?

- Reliability?

- Errors?

## **Protocol Analyzer sees nothing?**

- Is there a signal present? •

- Connect the analyzer probe output to an Oscilloscope to verify.

## **Protocol Analyzer sees nothing?**

- Is there a signal present?

- Connect the analyzer probe output to an Oscilloscope to verify.

### **Protocol Issues – Look at upper layers**

| Index | Direction | Time     | Host0    | Device1  | Power Mode | Error | MIBAttribute | Mibvalue |

|-------|-----------|----------|----------|----------|------------|-------|--------------|----------|

| 251   | Sublink1  | 16.42751 |          | TRG_UPR2 | PWM-G1 x1  | NONE  |              |          |

| 252   | Sublink1  | 16.42751 |          | TRG_UPR2 | PWM-G1 x1  | NONE  |              |          |

| 253   | Sublink0  | 16.42751 | Filler   |          | PWM-G1 x1  | NONE  |              |          |

| 254   | Sublink1  | 16.42752 |          | TRG_UPR2 | PWM-G1 x1  | NONE  |              |          |

| 255   | Sublink0  | 16.42752 | TRG_UPR1 |          | PWM-G1 x1  | NONE  |              |          |

| 256   | Sublink1  | 16.42752 |          | TRG_UPR2 | PWM-G1 x1  | NONE  |              |          |

| 257   | Sublink0  | 16.42752 | Filler   |          | PWM-G1 x1  | NONE  |              |          |

| 258   | Sublink1  | 16.42752 |          | TRG_UPR2 | PWM-G1 x1  | NONE  |              |          |

| 259   | Sublink1  | 16.42752 |          | TRG_UPR2 | PWM-G1 x1  | NONE  |              |          |

| 260   | Sublink0  | 16.42752 | TRG_UPR1 |          | PWM-G1 x1  | NONE  |              |          |

| 261   | Sublink1  | 16.42753 |          | TRG_UPR2 | PWM-G1 x1  | NONE  |              |          |

| 262   | Sublink0  | 16.42753 | Filler   |          | PWM-G1 x1  | NONE  |              |          |

| 263   | Sublink1  | 16.42753 |          | TRG_UPR2 | PWM-G1 x1  | NONE  |              |          |

| 264   | Sublink1  | 16.42753 |          | TRG_UPR2 | PWM-G1 x1  | NONE  |              |          |

| 265   | Sublink0  | 16.42753 | TRG_UPR1 |          | PWM-G1 x1  | NONE  |              |          |

| 266   | Sublink1  | 16.42753 |          | TRG_UPR2 | PWM-G1 x1  | NONE  |              |          |

| 267   | Sublink0  | 16.42753 | Filler   |          | PWM-G1 x1  | NONE  |              |          |

| 268   | Sublink1  | 16.42753 |          | TRG_UPR2 | PWM-G1 x1  | NONE  |              |          |

| 269   | Sublink0  | 16.42754 | TRG_UPR1 |          | PWM-G1 x1  | NONE  |              |          |

| 270   | Sublink1  | 16.42754 |          | TRG_UPR2 | PWM-G1 x1  | NONE  |              |          |

| 271   | Sublink1  | 16.42754 |          | TRG_UPR2 | PWM-G1 x1  | NONE  |              |          |

| 272   | Sublink0  | 16.42754 | Filler   |          | PWM-G1 x1  | NONE  |              |          |

| In test | Index | Direction | Time     | Host0                           | Device1                          | Power Mode |

|---------|-------|-----------|----------|---------------------------------|----------------------------------|------------|

|         | 4     | Sublink0  | 16.65201 | QUERY REQUEST (READ FLAG)       |                                  | PWM-G1 x1  |

|         | 5     | Sublink1  | 16.65222 |                                 | QUERY RESPONSE (READ FLAG)       | PWM-G1 x1  |

|         | 6     | Sublink0  | 16.70338 | QUERY REQUEST (READ FLAG)       |                                  | PWM-G1 x1  |

|         | 7     | Sublink1  | 16.70358 |                                 | QUERY RESPONSE (READ FLAG)       | PWM-G1 x1  |

|         | 8     | Sublink0  | 16.70470 | REQUEST SENSE                   |                                  | PWM-G1 x1  |

|         | 9     | Sublink1  | 16.70490 |                                 | REQUEST SENSE RESPONSE (DATA IN) | PWM-G1 x1  |

|         | 10    | Sublink1  | 16.70498 |                                 | RESPONSE                         | PWM-G1 x1  |

|         | 11    | Sublink0  | 16.70643 | REQUEST SENSE                   |                                  | PWM-G1 x1  |

|         | 12    | Sublink1  | 16.70663 |                                 | REQUEST SENSE RESPONSE (DATA IN) | PWM-G1 x1  |

|         | 13    | Sublink1  | 16.70672 |                                 | RESPONSE                         | PWM-G1 x1  |

|         | 14    | Sublink0  | 16.91731 | QUERY REQUEST (WRITE ATTRIBUTE) |                                  | PWM-G1 x1  |

|         | 15    | Sublink1  | 16.91779 |                                 | QUERY RESPONSE (WRITE ATTRIBUTE) | PWM-G1 x1  |

|         | 16    | Sublink0  | 17.64016 | WRITE (16)                      |                                  | HS-G3B x1  |

|         | 17    | Sublink1  | 17.64021 |                                 | READY TO TRANSFER                | HS-G3B x1  |

|         | 18    | Sublink0  | 17.64022 | WRITE (16) DATA (DATA OUT)      |                                  | HS-G3B x1  |

|         | 19    | Sublink1  | 17.64049 |                                 | RESPONSE                         | HS-G3B x1  |

|         | 20    | Sublink0  | 17.64089 | READ (16)                       |                                  | HS-G3B x1  |

|         | 21    | Sublink1  | 17.64095 |                                 | READ (16) DATA (DATA IN)         | HS-G3B x1  |

|         | 22    | Sublink1  | 17.64107 |                                 | RESPONSE                         | HS-G3B x1  |

|         | 23    | Sublink0  | 17.64153 | WRITE (16)                      |                                  | HS-G3B x1  |

|         | 24    | Sublink1  | 17.64158 |                                 | READY TO TRANSFER                | HS-G3B x1  |

|         | 25    | Sublink0  | 17.64159 | WRITE (16) DATA (DATA OUT)      |                                  | HS-G3B x1  |

© 2018 MIPI Alliance, Inc.

## **MIPI UniPro<sup>®</sup> - Link Startup Sequence**

The Link Startup Sequence is a multi-phase handshake, which exchanges MIPI UniPro<sup>®</sup> trigger events to establish initial Link communication, in both directions, between two directly attached MIPI UniPro<sup>®</sup> Devices.

### Link Startup Sequence

#### Table 13 Link Startup Sequence

| Phase | PA Transmitter                                                                                                                                    | PA Receiver                                                                                                                                  |  |  |  |  |  |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 0     | Continue to send TRG_UPR0 (all available Lanes)                                                                                                   | Wait for TRG_UPR0 reception. Lane discovery (see <i>Section 5.7.8.2</i> )                                                                    |  |  |  |  |  |

| 0b    | Send two additional TRG_UPR0 (all available Lanes)                                                                                                | Ignore all data                                                                                                                              |  |  |  |  |  |

|       | Then proceed with phase 1                                                                                                                         |                                                                                                                                              |  |  |  |  |  |

| 1     | Continue to send TRG_UPR1                                                                                                                         | Wait for TRG_UPR1 reception on all Lanes                                                                                                     |  |  |  |  |  |

|       |                                                                                                                                                   | Re-align Lane numbering (Section 5.7.8.3)                                                                                                    |  |  |  |  |  |

| 2     | Send two additional TRG_UPR1                                                                                                                      | Ignore all data                                                                                                                              |  |  |  |  |  |

|       | Then proceed with phase 3                                                                                                                         |                                                                                                                                              |  |  |  |  |  |

| 3     | Continue to send TRG_UPR2 on all Lanes                                                                                                            | Wait for TRG_UPR2 reception on PHY RX<br>Data Lane 0<br>• TRG_UPR2 (-> advance to phase 4)<br>• TRG_UPR1 (-> ignore)<br>• Others (-> ignore) |  |  |  |  |  |

| 4     | Send two additional TRG_UPR2 on all Lanes<br>Then proceed with Phase 5                                                                            | Ignore all data                                                                                                                              |  |  |  |  |  |

| 5     | Transfer Capabilities                                                                                                                             | Receive Capabilities and apply down grading                                                                                                  |  |  |  |  |  |

|       | Report to the DME using PA_LM_LINKSTARTUP.cnf_L that the Link Startup Sequence succeeded. Exit the Link Startup Sequence and enter SlowAuto_Mode. |                                                                                                                                              |  |  |  |  |  |

MIPI ALLIANCE DEVELOPERS CONFERENCE 19 OCTOBER 2018 **SEOUL**

#### © 2018 MIPI Alliance, Inc.

### **MIPI UniPro<sup>®</sup> - Link Startup Sequence**

• Do both sides go through the Link Startup Sequence?

| 8164 | Sublink0 | 58.23605 |            | TRG_UPR1   | PWM-G1 x1 | NONE | MIPI A<br>DEVEI |

|------|----------|----------|------------|------------|-----------|------|-----------------|

| 8163 | Sublink0 | 58.23605 |            | TRG_UPR1   | PWM-G1 x1 | NONE | -               |

| 8162 | Sublink0 | 58.23604 |            | TRG_UPR1   | PWM-G1 x1 | NONE |                 |

| 8161 | Sublink0 | 58.23604 |            | TRG_UPR0   | PWM-G1 x1 | NONE |                 |

| 8160 | Sublink0 | 58.23604 |            | TRG_UPR0   | PWM-G1 x1 | NONE |                 |

| 8159 | Sublink0 | 58.23604 |            | TRG_UPR0   | PWM-G1 x1 | NONE |                 |

| 8152 | Sublink1 | 58.23537 | TRG_UPR0   |            | PWM-G1 x1 | NONE |                 |

| 8144 | Sublink0 | 58.23446 |            | TRG_UPR0   | PWM-G1 x1 | NONE |                 |

| 8137 | Sublink1 | 58.23337 | TRG_UPR0   |            | PWM-G1 x1 | NONE |                 |

| 8129 | Sublink0 | 58.23289 |            | TRG_UPR0   | PWM-G1 x1 | NONE |                 |

| 8123 | Sublink1 | 58.23130 | TRG_UPR0   |            | PWM-G1 x1 | NONE |                 |

| 8119 | Sublink0 | 58.23052 |            | Line-Reset | PWM-G1 x1 | NONE |                 |

| 8115 | Sublink1 | 58.22923 | TRG_UPR0   |            | PWM-G1 x1 | NONE |                 |

| 8107 | Sublink1 | 58.22716 | TRG_UPR0   |            | PWM-G1 x1 | NONE |                 |

| 8104 | Sublink1 | 57.83088 | Line-Reset |            | PWM-G1 x1 | NONE |                 |

ONFERENCE

## MIPI UniPro<sup>®</sup> – Link Startup Sequence

• Does the Link Startup Sequence Complete?

| 8925 Sublink1 58.23783 TRG_UPR2 PWM-G1 x1 NONE   8926 Sublink1 58.23783 TRG_UPR2 PWM-G1 x1 NONE   8927 Sublink1 58.23784 TRG_UPR2 PWM-G1 x1 NONE   8927 Sublink1 58.23784 TRG_UPR2 PWM-G1 x1 NONE   8928 Sublink1 58.23784 TRG_UPR2 PWM-G1 x1 NONE   8929 Sublink1 58.23785 TRG_UPR2 PWM-G1 x1 NONE   8930 Sublink1 58.23785 TRG_UPR2 PWM-G1 x1 NONE   8930 Sublink0 58.23807 TRG_UPR2 PWM-G1 x1 NONE   8939 Sublink0 58.23807 TRG_UPR2 PACP_CAP_EXT1_ind PWM-G1 x1 NONE   8940 Sublink0 58.23807 TRG_UPR2 PACP_CAP_EXT1_ind PWM-G1 x1 NONE   8947 Sublink1 58.2387 PACP_CAP_EXT1_ind PWM-G1 x1 NONE   8949 Sublink1 58.2387      |      |          |          |                   |                   |           |      |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|----------|----------|-------------------|-------------------|-----------|------|

| 8927 Sublink1 58.23784 TRG_UPR2 PWM-G1 x1 NONE   8928 Sublink1 58.23784 TRG_UPR2 PWM-G1 x1 NONE   8929 Sublink1 58.23784 TRG_UPR2 PWM-G1 x1 NONE   8929 Sublink1 58.23784 TRG_UPR2 PWM-G1 x1 NONE   8930 Sublink1 58.23785 TRG_UPR2 PWM-G1 x1 NONE   8930 Sublink0 58.23875 TRG_UPR2 PWM-G1 x1 NONE   8930 Sublink0 58.23807 TRG_UPR2 PACP_CAP_EXT1_ind PWM-G1 x1 NONE   8940 Sublink0 58.23807 TRG_UPR2 PACP_CAP_EXT1_ind PWM-G1 x1 NONE   8947 Sublink1 58.23867 PACP_CAP_EXT1_ind PWM-G1 x1 NONE   8949 Sublink1 58.23875 PACP_CAP_ind PWM-G1 x1 NONE   8960 Sublink0 58.23948 AFC TC1 PWM-G1 x1 NONE   8961 Sublink0 58.23948 | 8925 | Sublink1 | 58.23783 | TRG_UPR2          |                   | PWM-G1 x1 | NONE |

| 8928 Sublink1 58.23784 TRG_UPR2 PWM-G1 x1 NONE   8929 Sublink1 58.23784 TRG_UPR2 PWM-G1 x1 NONE   8930 Sublink1 58.23785 TRG_UPR2 PWM-G1 x1 NONE   8930 Sublink0 58.23785 TRG_UPR2 PWM-G1 x1 NONE   8939 Sublink0 58.23807 TRG_UPR2 PWM-G1 x1 NONE   8939 Sublink0 58.23807 TRG_UPR2 PWM-G1 x1 NONE   8940 Sublink0 58.23807 PACP_CAP_EXT1_ind PWM-G1 x1 NONE   8947 Sublink1 58.23867 PACP_CAP_EXT1_ind PWM-G1 x1 NONE   8949 Sublink1 58.23875 PACP_CAP_ind PWM-G1 x1 NONE   8960 Sublink0 58.23948 PACP_CAP_ind PWM-G1 x1 NONE   8961 Sublink0 58.23948 AFC TC1 PWM-G1 x1 NONE   8970 Sublink1 58.24024 AFC TC1 PWM-G1 x1      | 8926 | Sublink1 | 58.23783 | TRG_UPR2          |                   | PWM-G1 x1 | NONE |

| 8929 Sublink1 58.23784 TRG_UPR2 PWM-G1 x1 NONE   8930 Sublink1 58.23785 TRG_UPR2 PWM-G1 x1 NONE   8939 Sublink0 58.23807 TRG_UPR2 PACP_CAP_EXT1_ind PWM-G1 x1 NONE   8939 Sublink0 58.23807 TRG_UPR2 PACP_CAP_EXT1_ind PWM-G1 x1 NONE   8940 Sublink0 58.23807 PACP_CAP_EXT1_ind PACP_CAP_ind PWM-G1 x1 NONE   8947 Sublink1 58.23875 PACP_CAP_EXT1_ind PWM-G1 x1 NONE   8949 Sublink1 58.23875 PACP_CAP_ind PWM-G1 x1 NONE   8960 Sublink0 58.23948 PACP_CAP_ind PWM-G1 x1 NONE   8961 Sublink0 58.23948 AFC TC1 PWM-G1 x1 NONE   8970 Sublink1 58.24024 AFC TC1 PWM-G1 x1 NONE                                                  | 8927 | Sublink1 | 58.23784 | TRG_UPR2          |                   | PWM-G1 x1 | NONE |

| 8930 Sublink1 58.23785 TRG_UPR2 PWM-G1 x1 NONE   8939 Sublink0 58.23807 PACP_CAP_EXT1_ind PWM-G1 x1 NONE   8940 Sublink0 58.23807 PACP_CAP_EXT1_ind PWM-G1 x1 NONE   8940 Sublink0 58.23810 PACP_CAP_EXT1_ind PWM-G1 x1 NONE   8947 Sublink1 58.23867 PACP_CAP_EXT1_ind PWM-G1 x1 NONE   8949 Sublink1 58.23867 PACP_CAP_EXT1_ind PWM-G1 x1 NONE   8949 Sublink1 58.23875 PACP_CAP_ind PWM-G1 x1 NONE   8960 Sublink0 58.23948 PACP_CAP_ind PWM-G1 x1 NONE   8961 Sublink0 58.23948 AFC TC0 PWM-G1 x1 NONE   8970 Sublink1 58.24024 AFC TC1 PWM-G1 x1 NONE                                                                        | 8928 | Sublink1 | 58.23784 | TRG_UPR2          |                   | PWM-G1 x1 | NONE |

| 8939 Sublink0 58.23807 PACP_CAP_EXT1_ind PWM-G1 x1 NONE   8940 Sublink0 58.23810 PACP_CAP_ind PWM-G1 x1 NONE   8947 Sublink1 58.23807 PACP_CAP_EXT1_ind PWM-G1 x1 NONE   8947 Sublink1 58.23875 PACP_CAP_EXT1_ind PWM-G1 x1 NONE   8949 Sublink1 58.23875 PACP_CAP_ind PWM-G1 x1 NONE   8960 Sublink0 58.23948 PACP_CAP_ind PWM-G1 x1 NONE   8961 Sublink0 58.23948 AFC TC1 PWM-G1 x1 NONE   8970 Sublink1 58.24024 AFC TC1 PWM-G1 x1 NONE                                                                                                                                                                                        | 8929 | Sublink1 | 58.23784 | TRG_UPR2          |                   | PWM-G1 x1 | NONE |

| 8940 Sublink0 58.23810 PACP_CAP_ind PWM-G1 x1 NONE   8947 Sublink1 58.23867 PACP_CAP_EXT1_ind PWM-G1 x1 NONE   8949 Sublink1 58.23875 PACP_CAP_ind PWM-G1 x1 NONE   8960 Sublink0 58.23948 PACP_CAP_ind PWM-G1 x1 NONE   8961 Sublink0 58.23948 AFC TC1 PWM-G1 x1 NONE   8961 Sublink1 58.23948 AFC TC0 PWM-G1 x1 NONE   8970 Sublink1 58.24024 AFC TC1 PWM-G1 x1 NONE                                                                                                                                                                                                                                                            | 8930 | Sublink1 | 58.23785 | TRG_UPR2          |                   | PWM-G1 x1 | NONE |

| 8947 Sublink1 58.23867 PACP_CAP_EXT1_ind PWM-G1 x1 NONE   8949 Sublink1 58.23875 PACP_CAP_ind PWM-G1 x1 NONE   8960 Sublink0 58.23948 PACP_CAP_ind AFC TC1 PWM-G1 x1 NONE   8961 Sublink0 58.23948 AFC TC0 PWM-G1 x1 NONE   8970 Sublink1 58.24024 AFC TC1 PWM-G1 x1 NONE                                                                                                                                                                                                                                                                                                                                                         | 8939 | Sublink0 | 58.23807 |                   | PACP_CAP_EXT1_ind | PWM-G1 x1 | NONE |

| 8949 Sublink1 58.23875 PACP_CAP_ind PWM-G1 x1 NONE   8960 Sublink0 58.23948 AFC TC1 PWM-G1 x1 NONE   8961 Sublink0 58.23948 AFC TC0 PWM-G1 x1 NONE   8970 Sublink1 58.24024 AFC TC1 PWM-G1 x1 NONE                                                                                                                                                                                                                                                                                                                                                                                                                                | 8940 | Sublink0 | 58.23810 |                   | PACP_CAP_ind      | PWM-G1 x1 | NONE |

| 8960 Sublink0 58.23948 AFC TC1 PWM-G1 x1 NONE   8961 Sublink0 58.23948 AFC TC0 PWM-G1 x1 NONE   8970 Sublink1 58.24024 AFC TC1 PWM-G1 x1 NONE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 8947 | Sublink1 | 58.23867 | PACP_CAP_EXT1_ind |                   | PWM-G1 x1 | NONE |

| 8961 Sublink0 58.23948 AFC TC0 PWM-G1 x1 NONE   8970 Sublink1 58.24024 AFC TC1 PWM-G1 x1 NONE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 8949 | Sublink1 | 58.23875 | PACP_CAP_ind      |                   | PWM-G1 x1 | NONE |

| 8970 Sublink1 58.24024 AFC TC1 PWM-G1 x1 NONE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 8960 | Sublink0 | 58.23948 |                   | AFC TC1           | PWM-G1 x1 | NONE |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 8961 | Sublink0 | 58.23948 |                   | AFC TC0           | PWM-G1 x1 | NONE |

| 8972 Sublink1 58.24029 AFC TC0 PWM-G1 x1 NONE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 8970 | Sublink1 | 58.24024 | AFC TC1           |                   | PWM-G1 x1 | NONE |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 8972 | Sublink1 | 58.24029 | AFC TC0           |                   | PWM-G1 x1 | NONE |

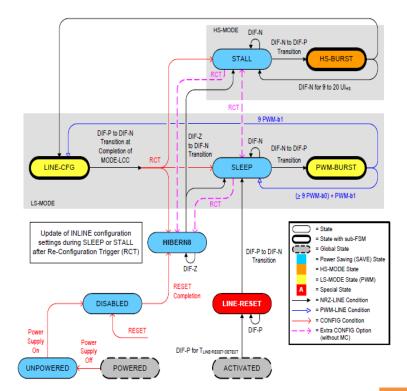

## **State Machine**

- Two operating modes,

- HS-MODE

- LS-MODE

- A data transmission (BURST) state and a MODE-specific power saving (SAVE) state

- STALL is the SAVE state of HS-MODE

- SLEEP is the SAVE state of LS-MODE

- HS-MODE: STALL, HS-BURST

- LS-MODE (Type-I MODULE): SLEEP, PWM-BURST, LINE-CFG

- LS-MODE (Type-II MODULE): SLEEP, SYS-BURST

MIPI ALLIANCE DEVELOPERS CONFERENCE 19 OCTOBER 2018 SEOUL

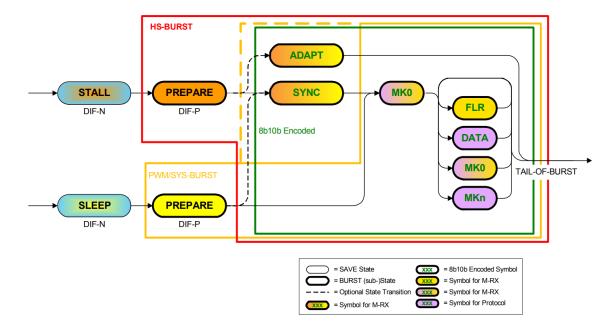

### **Bursts**

### • HSG4 includes ADAPT state

MIPI ALLIANCE DEVELOPERS CONFERENCE 19 OCTOBER 2018 **SEOUL**

© 2018 MIPI Alliance, Inc.

## **Power Mode Change**

- Are the Power Mode Changes happening as expected?

- Did the Link Startup Sequence Complete?

- Trigger on PACP\_PWR\_REQ to track Power mode changes

| Index | Direction Time    | Host         | Device       | Power Mode | Error | RxGear | RxLane | RxMode              | TxGear | TxLane | TxMode              |

|-------|-------------------|--------------|--------------|------------|-------|--------|--------|---------------------|--------|--------|---------------------|

| 1150  | Sublink1 6.169753 | PACP_PWR_req |              | PWM-G1 x1  | NONE  | 0x1    | 0x1    | FastAuto_Mode (0x4) | 0x1    | 0x1    | FastAuto_Mode (0x4) |

| 1156  | Sublink0 6.170045 |              | PACP_PWR_cnf | PWM-G1 x1  | NONE  | 0x1    | 0x1    | FastAuto_Mode (0x4) | 0x1    | 0x1    | FastAuto_Mode (0x4) |

39

## **UFS Initialization**

MIPI UniPro<sup>®</sup> Link Startup Sequence must complete before any UFS traffic can commence.

| In test | Index | Direction | Time             | Host                       | Device                    | Power Mode |

|---------|-------|-----------|------------------|----------------------------|---------------------------|------------|

|         | 0     | Sublink1  | 5.316020794000 s |                            | NOP OUT                   | PWM-G1 x1  |

|         | 1     | Sublink0  | 5.316397266000 s | NOP IN                     |                           | PWM-G1 x1  |

|         | 2     | Sublink1  | 5.383056086000 s |                            | QUERY REQUEST (SET FLAG)  | PWM-G1 x1  |

|         | 3     | Sublink0  | 5.383427540000 s | QUERY RESPONSE (SET FLAG)  |                           | PWM-G1 x1  |

|         | 4     | Sublink1  | 5.449256130000 s |                            | QUERY REQUEST (READ FLAG) | PWM-G1 x1  |

|         | 5     | Sublink0  | 5.449674915000 s | QUERY RESPONSE (READ FLAG) |                           | PWM-G1 x1  |

40

## Summary

- Although device is a UFS controller you are dependent on MIPI UniPro<sup>®</sup> Link Startup Sequence

- Knowing this process will help you understand how to bring up the device

- Identify Lower Layer issues first, otherwise nothing else will work

41

# mipi<sup>®</sup> DEVCON

### Q&A

MIPI ALLIANCE DEVELOPERS CONFERENCE

SEOUL

### ADDITIONAL RESOURCES

- MIPI M-PHY<sup>®</sup> Specification v4.0

- MIPI MIPI UniPro<sup>®</sup> Specification v1.8

- JEDEC Spec JESD220C (UFS)

# mipi DEVCON THANK YOU

### MIPI ALLIANCE DEVELOPERS CONFERENCE

SEOUL