#### Imaging interface advancements and development to meet the needs of mobile and mobile-influenced industries

February 17, 2016

Haran Thanigasalam Intel Senior Platform Architect | MIPI Camera WG Chair

# S About MIPI Alliance

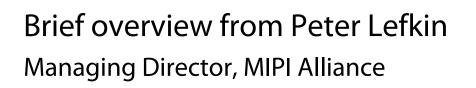

We are a global, collaborative organization comprised of over 280 member companies spanning the mobile and mobile-influenced ecosystems.

MIPI Alliance is leading innovation in mobile interface technology.

# MIPI Alliance Member Ecosystem

mipi<sup>alliance</sup>

mipialliance

Copyright © 2016 MIPI Alliance. All rights reserved.

# Overview

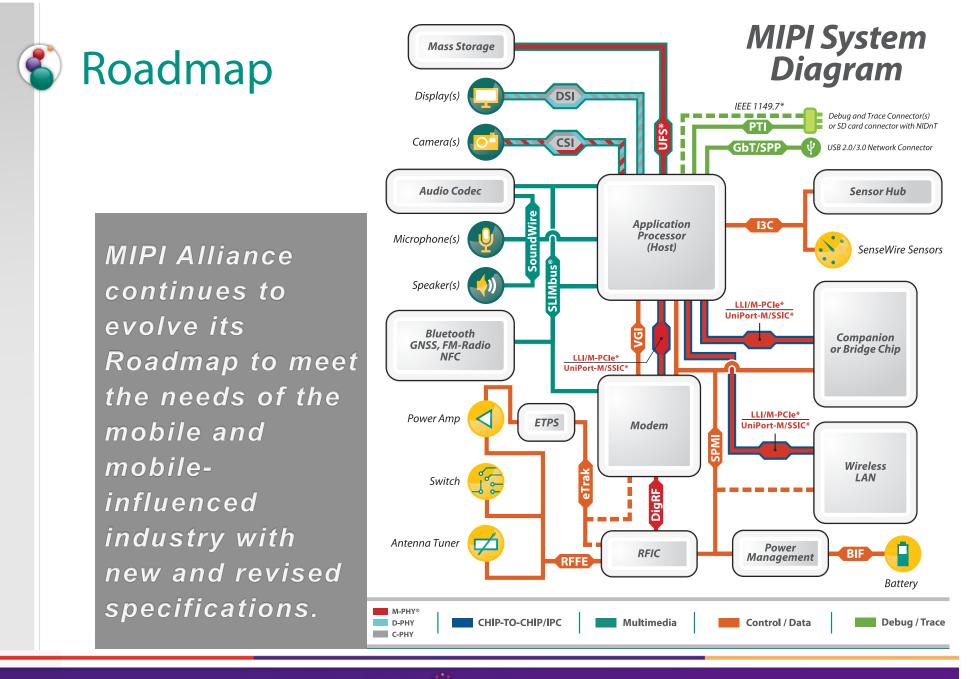

Generational advancements and development of MIPI CSI imaging interface to meet the needs of Mobile and beyond applications including:

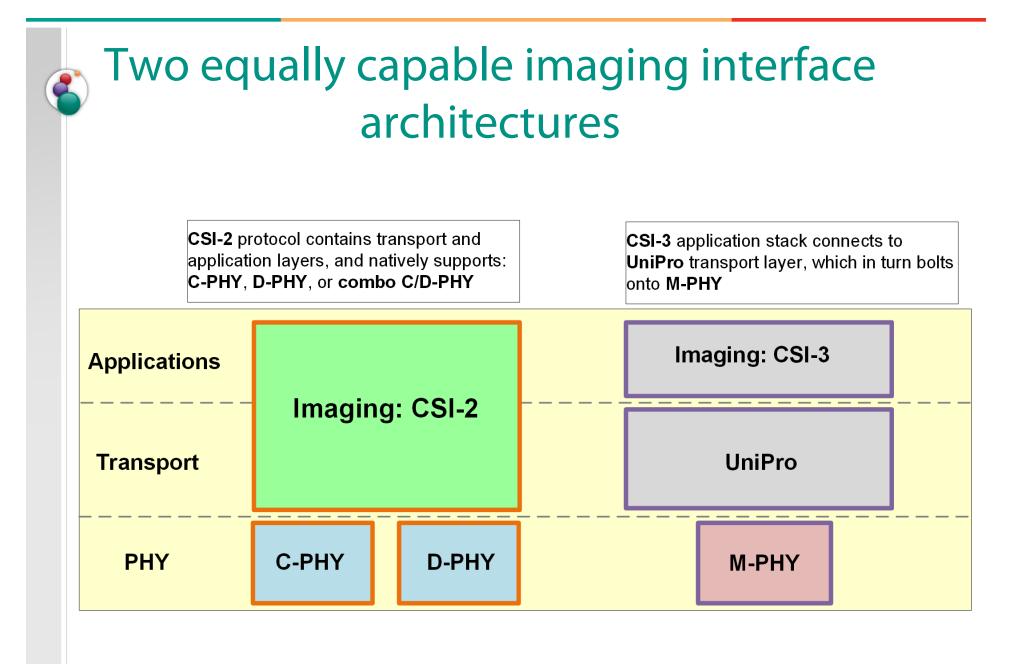

- Two equally capable MIPI imaging interface architectures

- CSI-2 over C/D-PHYs

- CSI-3 over UniPro and M-PHY

- Provision to mitigate PSD emissions

- Extended Virtual Channels

- High Dynamic Range enhancements

- Latency Reduction and Transport Efficiency

- Always On Metadata and Pixel Transfer

- Differential Pulse Code Modulation

### Imaging Development

# Solutions for popular imaging use case

|                              | 4K @ 3               | 0 fps and 12          | BPP using CS   | -2                    |                      |

|------------------------------|----------------------|-----------------------|----------------|-----------------------|----------------------|

| Required MIPI<br>Specs (IPs) | Required<br>PHY pins | Required<br>Lane Rate | Required<br>BW | Variable<br>Link Rate | Control<br>Interface |

| [CSI-2]<br>[D-PHY]           | 6                    | 1.78 Gbps             | 3.56 Gbps      | Yes                   | I2C                  |

| [CSI-2]<br>[C-PHY]           | 3                    | 1.55 Gsps             | 3.56 Gbps      | Yes                   | I2C                  |

|                                | 4K @ 3               | 0 fps and 12          | BPP using CS   | -3                    |                      |

|--------------------------------|----------------------|-----------------------|----------------|-----------------------|----------------------|

| Required MIPI<br>Specs (IPs)   | Required<br>PHY pins | Required<br>Lane Rate | Required<br>BW | Variable<br>Link Rate | Control<br>Interface |

| [CSI-3]<br>[UniPro]<br>[M-PHY] | 4                    | 5.0 Gbps              | 3.56 Gbps      | No                    | In-band              |

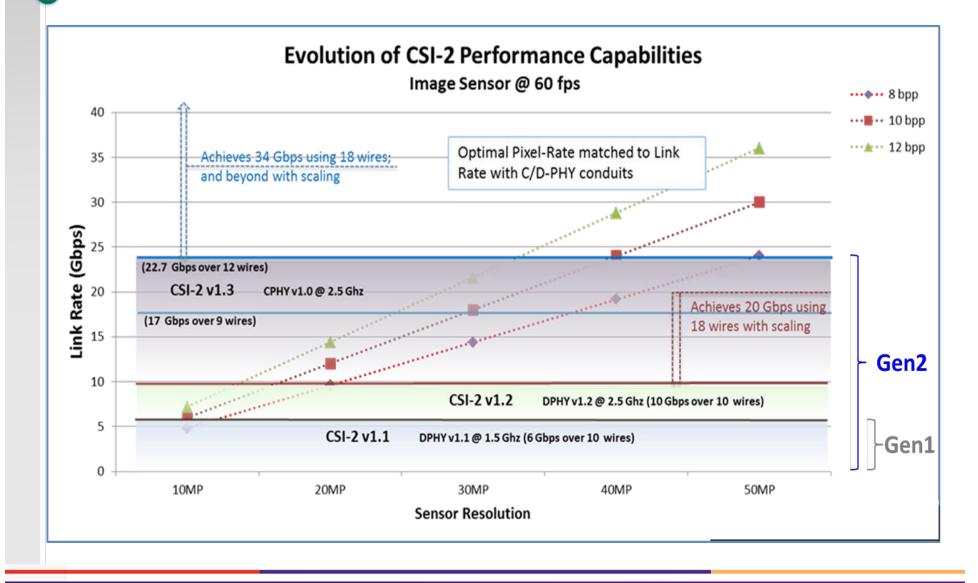

#### CSI-2 v1.3 over C/D-PHY Evolution & Performance

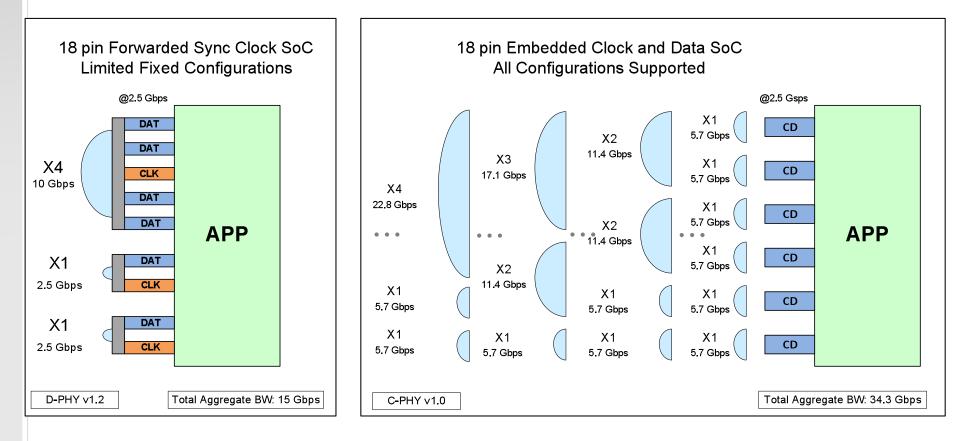

# CSI-2 Benefits of Embedded Clock & Data

- Multiple port configurations are required to map Imaging Use Cases

- CSI-2 v1.3 provides Logical Port realizations with embedded clock & data

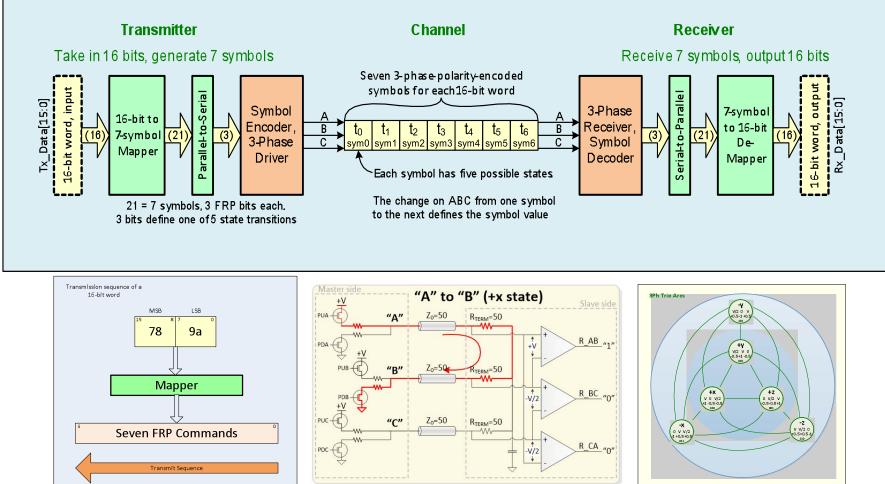

# SCSI-2 over C-PHY (N-Phase) Data Path

#### Triode Data Path

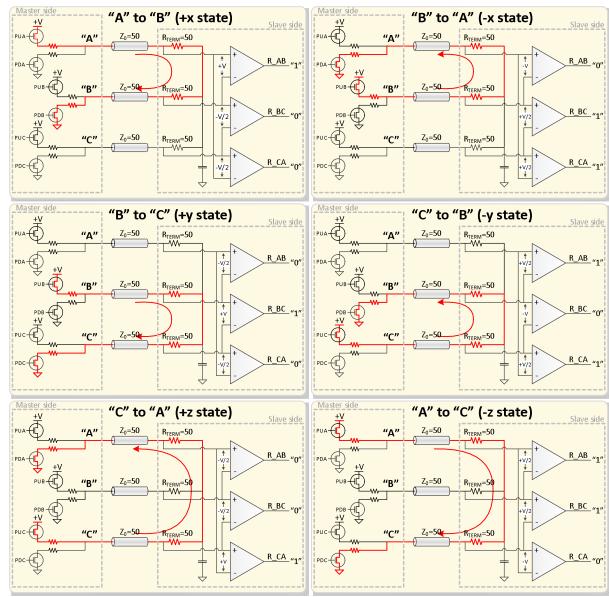

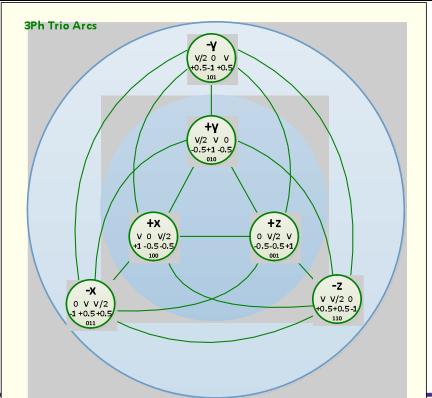

#### N-Phase (CSI-2 over C-PHY): 6 states using 3 wires

mipralliance

| Trio  | Wire | e Ampli | tude | Receive | r diff input | t voltage | Receiv | er digital | output |

|-------|------|---------|------|---------|--------------|-----------|--------|------------|--------|

| State | Α    | В       | С    | A - B   | B - C        | C - A     | Rx_AB  | Rx_BC      | Rx_CA  |

| +x    | +V   | 0       | +V/2 | +V      | -V/2         | -V/2      | 1      | 0          | 0      |

| -x    | 0    | +V      | +V/2 | -V      | +V/2         | +V/2      | 0      | 1          | 1      |

| +у    | +V/2 | +V      | 0    | -V/2    | +V           | -V/2      | 0      | 1          | 0      |

| -y    | +V/2 | 0       | +V   | +V/2    | -V           | +V/2      | 1      | 0          | 1      |

| +z    | 0    | +V/2    | +V   | -V/2    | -V/2         | +V        | 0      | 0          | 1      |

| -Z    | +V   | +V/2    | 0    | +V/2    | +V/2         | -V        | 1      | 1          | 0      |

mipralliance

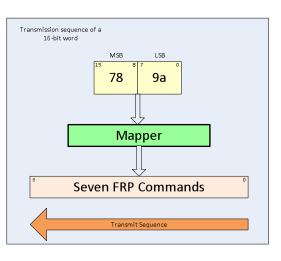

#### N-Phase: 16-bit to 7 FRP command mapping

|                      | Composition of 16-bit value, Tx Data[15:0] or Rx Data[15:0]                                                                  |

|----------------------|------------------------------------------------------------------------------------------------------------------------------|

| (1024) 6,4           | ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓                                                                                        |

| (1024) 5,4           | Control to Control in proportional [1,1,1,1,1,1,1,1,1,1,1,1,1,1,1,1,1,1,1,                                                   |

| (1024) 6, 3          | Child to 0x47ff Flip[60]=0x48=[1,0,0,1,0,0] [1,1,1,1,0,1, r.05, po5, r.04, po4, r.02, po2, r.01, po1, r.00, po0]             |

| 1024 ) 5, 3          | Current Control of Control of File(6:0)==0x28==[0,10,1,00,0] [1,1,1,1,0,0, ro6, po6, ro4, po4, ro2, po2, ro1, po1, ro0, po0] |

| <b>1024</b> ) 4, 3   | ▲ Oxec00 to 0xefff Flip[6:0]==0x18==[0.0.1.1.0.0.0] [1,1,1,2,0,1,1, ro6, po6, ro5, po5, ro2, po2, ro1, po1, ro0, po0]        |

| 1024) 6,2            | 4 0xe800 to 0xebff Flip[6:0]==0x44==[1,0,0,0,1,0,0] [1,1,1,0,1,0, ro5, po5, ro4, po4, ro3, po3, ro1, po1, ro0, po0]          |

| 1024 ) 5, 2          | 0xe400 to 0xe7ff Flip[6:0]==0x24==[0,10,0,1,0,0] [1,1,1,0,0,1, ro6, po6, ro4, po4, ro3, po3, ro1, po1, ro0, po0]             |

| 1024 ) 4, 2          | ▲ 0xe000 to 0xe3ff Flip[6:0]==0x14==[0,0,1,0,1,0,0] [1,1,1,0,0,0, ro6, ro5, ro5, ro5, ro3, ro1, ro1, ro1, ro0, ro0]          |

| ( <b>1024</b> ) 3, 2 | ← 0xdc00 to 0xdfff Flip[6:0]==0x0c==[0,0,0,1,1,0,0] [1,1,0,1,1,1, ro6, po6, ro5, po5, ro4, po4, ro1, po1, ro0, po0]          |

| ( <b>1024 )</b> 6, 1 | ▲ 0xd800 to 0xdbff Flip[6:0]==0x42==[1,0,0,0,0,1,0] [1,1,0,1,1,0, ro5, ro5, ro4, ro3, ro3, ro2, ro2, ro0, ro0]               |

| ; <b>1024 )</b> 5,1  | ← 0xd400 to 0xd7ff Flip[6:0]==0x22==[0,10,0,0,1,0] [1,1,0,1,0,1, ro6, po6, ro4, po4, ro3, po3, ro2, po2, ro0, po0]           |

| ( <b>1024</b> ) 4,1  | • 0xd000 to 0xd3ff Flip[6:0]==0x12==[0,0,1,0,0,1,0] [1,1,0,1,0,0, ro6, ro5, ro5, ro5, ro3, ro2, ro2, ro2, ro0, ro0]          |

| ( <b>1024</b> ) 3,1  | ← 0xcc00 to 0xcfff Flip[6:0]==0x0a==[0,0,0,1,0,1,0] [1,1,0,0,1,1,1, ro6, po6, ro5, po5, ro4, po4, ro2, po2, ro0, po0]        |

| ( <b>1024</b> ) 2,1  | ← 0xc800 to 0xcbff Flip[6:0]==0x06==[0,0,0,0,1,1,0] [1,1,0,0,1,0, ro6, po6, ro5, po5, ro4, po4, ro3, po3, ro0, po0]          |

| ( <b>1024</b> ) 6,0  | 0xc400 to 0xc7ff Flip[6:0]==0x41==[1,0,0,0,0,0,1] [1,1,0,0,0,1, ro5, po5, ro4, po4, ro3, po3, ro2, po2, ro1, po1]            |

| ( <b>1024</b> ) 5,0  | 0xc000 to 0xc3ff Flip[6:0]==0x21==[0,1,0,0,0,0,1] [1,1,0,0,0,0, ro6, ro4, ro4, ro3, ro3, ro2, ro2, ro1, ro1]                 |

| ( <b>1024</b> ) 4,0  | 0xbc00 to 0xbfff Flip[6:0]==0x11==[0.0,1.0.0.0.1] [1,0,1,1,1,1, ro6, po6, ro5, po5, ro3, po3, ro2, po2, ro1, po1]            |

| ( <b>1024</b> ) 3,0  | → 0xb800 to 0xbbff Filp[6:0]==0x09==[0.00.1,0.0.1] [1,0,1,1,1,0, ro6, ro5, ro5, ro5, ro4, ro4, ro2, ro1, ro1]                |

| ( <b>1024</b> ) 2,0  | ▲ 0xb400 to 0xb7ff Filp[6:0]==0x05==[0.00.0,10.1] [1,0,1,1,0,1, ro6, po6, ro5, po5, ro4, po4, ro3, po3, ro1, po1]            |

| ( <b>1024)</b> 1,0   | → 0xb000 to 0xb3ff Flip[6:0]==0x03==[0,0,0,0,1,1] [1,0,1,1,0,0, ro6, ro5, ro5, ro5, ro4, ro4, ro3, ro2, ro2, ro2]            |

|                      |                                                                                                                              |

| 4096) 6              | Flip[6:0]==0x40==[1,0,0,0,0,0]                                                                                               |

|                      | [1,0,1,0, ro5, po5, ro4, po4, ro3, po3, ro2, po2, ro1, po1, ro0, po0]                                                        |

|                      | 0xa000<br>0x9fff                                                                                                             |

| _                    | Flip[6:0]==0x20==[0,1,0,0,0,0,0]                                                                                             |

| (4096) 5             |                                                                                                                              |

|                      | [1,0,0,1, ro6, po6, ro4, po4, ro3, po3, ro2, po2, ro1, po1, ro0, po0]<br>0x9000                                              |

|                      | 0x8fff                                                                                                                       |

|                      | Flip[6:0]==0x10==[0,0,1,0,0,0,0]                                                                                             |

| (4096) 4             | [1,0,0,1,0,0,1,0,0,0,0,0,0,0,0,0,0,0,0,0                                                                                     |

|                      | 0x8000                                                                                                                       |

|                      | 0x/fff                                                                                                                       |

| 0                    | Flip[6:0]==0x08==[0,0,0,1,0,0,0]                                                                                             |

| ( <b>4096)</b> 3     | [0,1,1,1, ro6, po6, ro5, po5, ro4, po4, ro2, po2, ro1, po1, ro0, po0]                                                        |

|                      | 0x7000                                                                                                                       |

|                      | 0x6fff                                                                                                                       |

|                      | Flip[6:0]==0x04==[0,0,0,0,1,0,0]                                                                                             |

| (4096) 2             | [0,1,1,0, ro6, po6, ro5, po5, ro4, po4, ro3, po3, ro1, po1, ro0, po0]                                                        |

|                      | 0x6000                                                                                                                       |

|                      | 0x5fff                                                                                                                       |

|                      | Flip[6:0]==0x02==[0,0,0,0,0,1,0]                                                                                             |

| (4096) 1             | [0,1,0,1, ro6, po6, ro5, po5, ro4, po4, ro3, po3, ro2, po2, ro0, po0]                                                        |

|                      | 0x5000                                                                                                                       |

|                      | 0x4fff                                                                                                                       |

|                      | Flip[6:0]==0x01==[0,0,0,0,0,0,1]                                                                                             |

| (4096) ()            | [0,1,0,0, ro6, po6, ro5, po5, ro4, po4, ro3, po3, ro2, po2, ro1, po1]                                                        |

|                      | 0x4000                                                                                                                       |

|                      | 0x3fff                                                                                                                       |

|                      |                                                                                                                              |

|                      | Flip[6:0]==0x00==[0,0,0,0,0,0]                                                                                               |

|                      | [0,0, ro6, po6, ro5, po5, ro4, po4, ro3, po3, ro2, po2, ro1, po1, ro0, po0]                                                  |

|                      |                                                                                                                              |

|                      | Legend for abbreviated bit values above                                                                                      |

| (0 6 or 5            | Legend for abbreviated bit values above:                                                                                     |

| (0 – 6 are           | $ro0 \Rightarrow Rotate[0]$ $po0 \Rightarrow Polarity[0]$                                                                    |

|                      | $ro1 \Rightarrow Rotate[1]$ $po1 \Rightarrow Polarity[1]$                                                                    |

| all zero)            | $ro2 \Rightarrow Rotate[2]$ $po2 \Rightarrow Polarity[2]$                                                                    |

| all zero)            |                                                                                                                              |

| all zero)            | $ro3 \Rightarrow Rotate[3]$ $po3 \Rightarrow Polarity[3]$                                                                    |

| all zero)            |                                                                                                                              |

| all zero)            | $ro4 \Rightarrow Rotate[4]$ $po4 \Rightarrow Polarity[4]$                                                                    |

| all zero)            |                                                                                                                              |

Copyright © 2016 MIPI Alliance. All rights reserved.

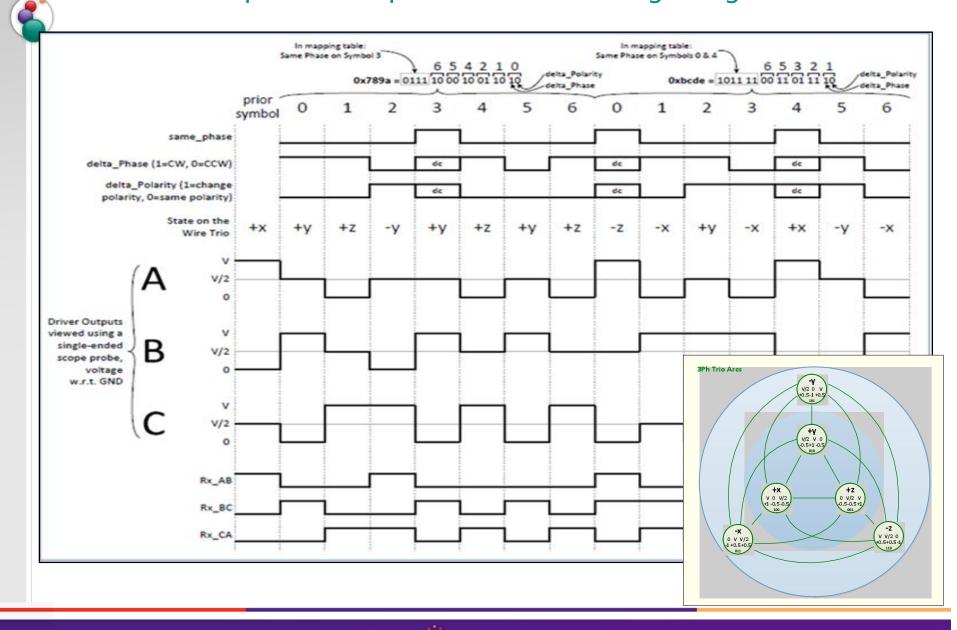

#### N-Phase: Example of CSI-2 pixel data to C-PHY signaling 1/2

| 16-bit | t Pix Data | Mapping | to symbols | ove | r 7 ( | UI | Encodi | ng to Wi | re Sta | te  |

|--------|------------|---------|------------|-----|-------|----|--------|----------|--------|-----|

| hex    | decimal    | Region  | Tx Sym     | F   | R     | Ρ  | State  | Α        | В      | С   |

|        |            |         |            |     |       |    | +x     | V        | 0      | V/2 |

| 789a   | 30874      | 3; 4K   | 2          | 0   | 1     | 0  | +y     | V/2      | V      | 0   |

|        |            |         | 2          | 0   | 1     | 0  | +z     | 0        | V/2    | V   |

|        |            |         | 1          | 0   | 0     | 1  | -у     | V/2      | 0      | V   |

|        |            |         | 4          | 1   | 0     | 0  | +y     | V/2      | V      | 0   |

|        |            |         | 2          | 0   | 1     | 0  | +z     | 0        | V/2    | V   |

|        |            |         | 0          | 0   | 0     | 0  | +y     | V/2      | V      | 0   |

|        |            |         | 2          | 0   | 1     | 0  | +z     | 0        | V/2    | V   |

| bcde   | 48350      | 4,0; 1K | 4          | 1   | 0     | 0  | -Z     | V        | V/2    | 0   |

|        |            |         | 2          | 0   | 1     | 0  | -x     | 0        | V      | V/2 |

|        |            |         | 3          | 0   | 1     | 1  | +у     | V/2      | V      | 0   |

|        |            |         | 1          | 0   | 0     | 1  | -x     | 0        | V      | V/2 |

|        |            |         | 4          | 1   | 0     | 0  | +x     | V        | 0      | V/2 |

|        |            |         | 3          | 0   | 1     | 1  | -у     | V/2      | 0      | V   |

|        |            |         | 0          | 0   | 0     | 0  | -x     | 0        | V      | V/2 |

#### N-Phase: Example of CSI-2 pixel data to C-PHY signaling 2/2

# N-Phase Mission Critical Transfers 1/2

Page 19

#### N-Phase mission critical transfers 2/2

|                             | Link Error Example (a): Loss of No Symbol Clocks |    |                       |        |         |        |    |                             |         |    |    |    |    |    |    |    |    |    |

|-----------------------------|--------------------------------------------------|----|-----------------------|--------|---------|--------|----|-----------------------------|---------|----|----|----|----|----|----|----|----|----|

|                             |                                                  |    | Symbol Interval       |        |         |        |    | TX: Transmit ESCAPE [s0:s6] |         |    |    |    |    |    |    |    |    |    |

| Transmitted Symbols         |                                                  | 2  | 2 1 3 2 1 3 0         |        |         |        | 3  | 4                           | 4       | 4  | 4  | 4  | 3  | 2  | 4  | 3  |    |    |

|                             |                                                  |    |                       |        |         |        |    |                             |         |    |    |    |    |    |    |    |    |    |

| Transmitted Wire States     | +z                                               | +X | x -z +x +y -x +y +x   |        |         |        | -у | +у                          | -у      | +y | -у | +у | -Z | -X | +x | -у |    |    |

|                             |                                                  |    |                       |        |         |        |    |                             |         |    |    |    |    |    |    |    |    |    |

| <b>Received Wire States</b> | +Z                                               | +X | -Z                    | +X     | +y      | -X     | +y | +Z                          | -у      | +у | -у | +у | -у | +y | -Z | -X | +x | -у |

|                             |                                                  |    | RX: Detect ESCAPE [s1 |        |         |        |    |                             | [s1:s6] |    |    |    |    |    |    |    |    |    |

| Received Symbols            |                                                  | 2  | 1 3 2 1 3 2           |        |         |        | 1  | 4                           | 4       | 4  | 4  | 4  | 3  | 2  | 4  | 3  |    |    |

|                             |                                                  | ←  |                       | 7 Rece | ived Sy | /mbols | s  |                             |         |    |    |    |    |    |    |    |    |    |

#### Link Error Example (b): Loss of One Symbol Clock

|                             |    | I  | Sym | bol Int | erval  |        |       |    | ←             | —TX: 1 |        | it ESC. | APE [s |         |    | 1  |    |    |

|-----------------------------|----|----|-----|---------|--------|--------|-------|----|---------------|--------|--------|---------|--------|---------|----|----|----|----|

|                             |    | L  |     | $\sim$  |        |        |       |    | s0            | s1     | s2     | s3      | s4     | s5      | s6 |    | -  |    |

| Transmitted Symbols         |    | 1  | 3   | 0       | 3      | 4      | 1     | 4  | 3             | 4      | 4      | 4       | 4      | 4       | 3  | 0  | 3  | 1  |

|                             |    |    |     |         |        |        |       |    |               |        |        |         |        |         |    |    |    |    |

| Transmitted Wire States     | +Z | -у | +Z  | +у      | -Z     | +Z     | -у    | +у | -Z            | +Z     | -Z     | +Z      | -Z     | +z      | -X | -Z | +X | -Z |

|                             |    |    |     |         |        |        |       |    |               |        |        |         |        |         |    |    |    |    |

| <b>Received Wire States</b> | +Z | -у | +Z  | +y      | -Z     | +Z     | -у    | -у | -Z            | +Z     | -Z     | +Z      | -Z     | +Z      | -X | +X | -у | -X |

|                             |    |    |     |         |        |        |       |    |               | ←      | RX: De | tect ES | SCAPE  | [s1:s6] |    |    |    |    |

| Received Symbols            |    | 1  | 3   | 0       | 3      | 4      | 1     | 1  | 2             | 4      | 4      | 4       | 4      | 4       | 3  | 0  | 3  | 1  |

|                             |    | k— |     | —7 R    | eceive | d Symb | ools— |    | $\rightarrow$ |        |        |         |        |         |    |    |    |    |

#### Link Error Example (c): Loss of Two Symbol Clocks

|                             |    |    | Sym | bol Int | erval  |         |        |    | <b>∢</b> | —TX:⁻<br>I ₅1 | Fransm<br>Is2 | nit ESC<br> _s3 | APE[s | 0:s6]—<br>Is5 | <b>5</b> 6 |    |    |    |

|-----------------------------|----|----|-----|---------|--------|---------|--------|----|----------|---------------|---------------|-----------------|-------|---------------|------------|----|----|----|

| Transmitted Symbols         |    | 4  | 3   | 1       | 2      | 0       | 1      | 1  | 3        | 4             | 4             | 4               | 4     | 4             | 3          | 0  | 2  | 4  |

|                             |    |    |     |         |        |         |        |    |          |               |               |                 |       |               |            |    |    |    |

| Transmitted Wire States     | +Z | -Z | +X  | -Z      | -X     | -Z      | +y     | -X | +y       | -у            | +y            | -у              | +y    | -у            | +z         | +y | +z | -Z |

|                             |    |    |     |         |        |         |        |    |          |               |               |                 |       |               |            |    |    |    |

| <b>Received Wire States</b> | +Z | -Z | +X  | -Z      | -X     | -Z      | +у     | +y | +y       | -у            | +y            | -у              | +y    | -у            | +z         | +y | +Z | -Z |

|                             |    |    |     |         |        |         |        |    |          | ◄             | RX: De        | tect ES         | CAPE  | [s1:s6]       |            |    |    |    |

| Received Symbols            |    | 4  | 3   | 1       | 2      | 0       | 1      | 1  | 1        | 4             | 4             | 4               | 4     | 4             | 3          | 0  | 2  | 4  |

|                             |    |    |     |         | 7 Rece | ived Sy | /mbols | s  |          |               |               |                 |       |               |            |    |    |    |

#### Notes:

- Symbols are transmitted serially from left to right

- Wire state and symbol errors are highlighted in yellow

- 🔺 : point at which symbol clock is lost

- 🔺 : point at which symbol clock is restored

- $\blacklozenge$ : point of incorrect word alignment

- $\blacklozenge$  : point at which correct word alignment is restored

## Evolution of CSI-2 Imaging Interface

| 6 | Imaging<br>Interface | Description<br>Interface Performance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Release /<br>Adoption |

|---|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

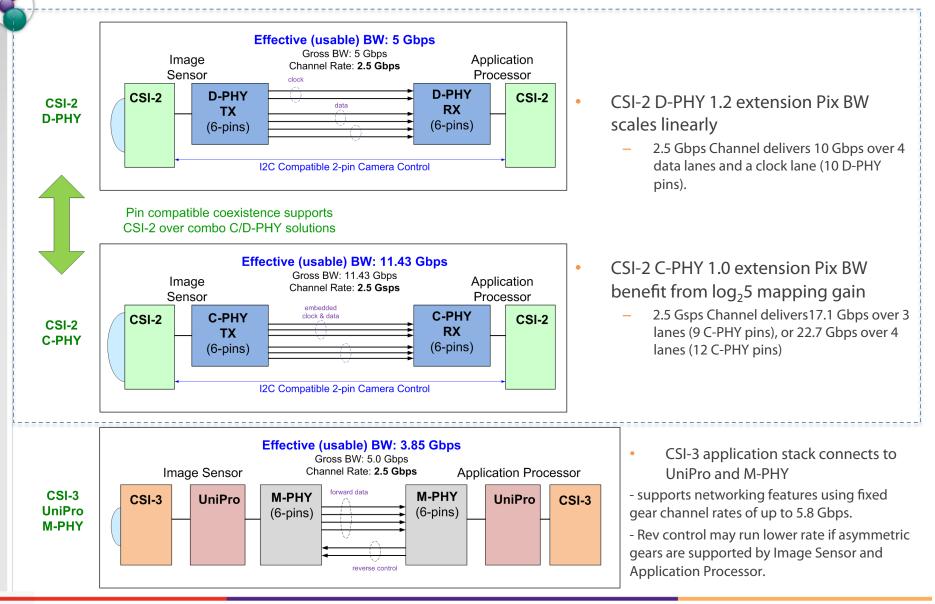

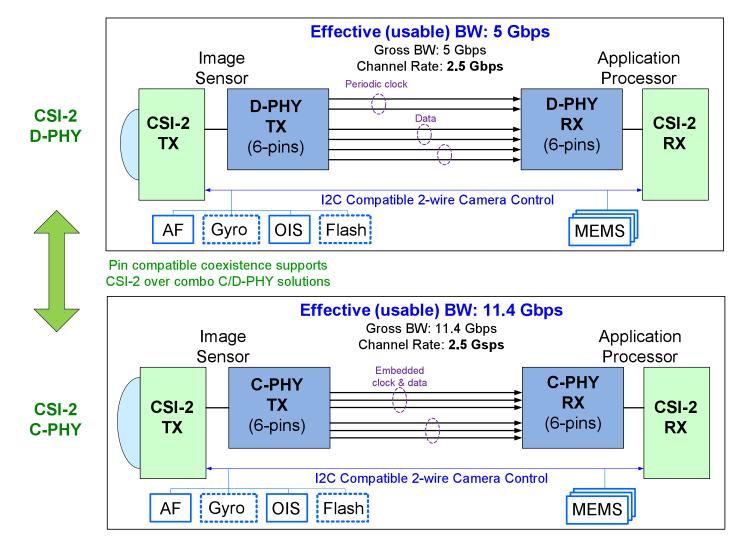

|   | Gen 1                | CSI-2 v1.1 protocol over D-PHY v1.1 (at 1.5 Gbps), and bidirectional command over I2C_FM (at 400 Kbps) Provides effective (usable) BW of 3 Gbps over 6 D-PHY v1.1 pins                                                                                                                                                                                                                                                                                                                                                                                                                            | EOY 2012              |

|   | Gen 2                | <ul> <li>CSI-2 v1.2 protocol over D-PHY v1.2 (at 2.5 Gbps), and bidirectional command over I2C_FM (at 400 Kbps)</li> <li>CSI-2 v1.3 protocol over C-PHY v1.0 (2.5 Gsps or 5.7 Gbps) and D-PHY v1.2 (at 2.5 Gbps), and bidirectional command over I2C_FM (at 400 Kbps)</li> <li>Provides effective (usable) BW of 5 Gbps over 6 D-PHY v1.2 pins<br/>Provides effective (usable) BW of 11.43 Gbps over 6 C-PHY v1.0 pins</li> </ul>                                                                                                                                                                 | EOY 2014              |

|   | Gen 3                | CSI-2 v2.0 protocol supports C-PHY v1.2 and D-PHY v2.1, with bidirectional command over<br>I2C_FMP (1GHz) and I3C v1.0.C-PHY v1.2 provides up to 4.5 Gsps (10.3 Gbps) over 3 pinsD-PHY v2.1 provides up to 4.5 Gbps over 4 pinsBidirectional CCI over I2C_FMP provides around 880 Kbps of effective BW, and CCI over I3C<br>v1.0 provides effective BW of: 10.67 Mbps over SDR, 19.2 Mbps over HDR-DDR, 18 Mbps<br>over HDR-TSL, and 29.3 Mbps over HDR-TSP.Provides effective (usable) BW of 9 Gbps over 6 D-PHY v2.1 pins<br>Provides effective (usable) BW of 20.6 Gbps over 6 C-PHY v1.2 pins | EOY 2016              |

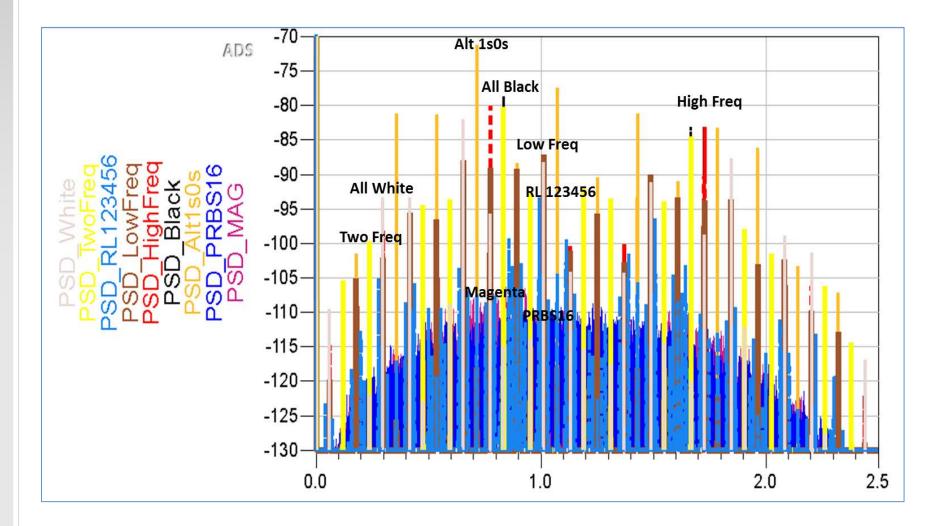

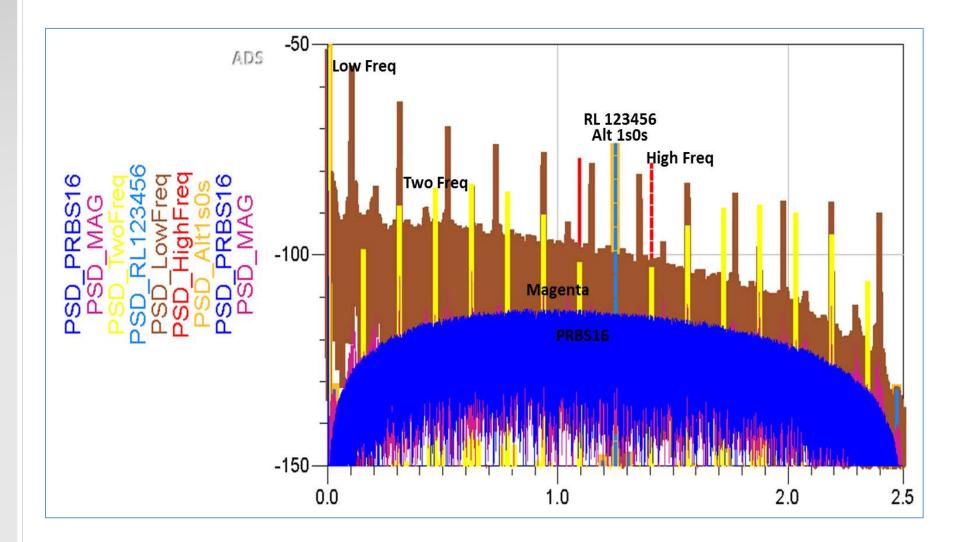

### CSI-2 over C-PHY PSD emission reduction from scrambling

### CSI-2 over D-PHY PSD emission reduction from scrambling

mipralliance

Copyright © 2016 MIPI Alliance. All rights reserved.

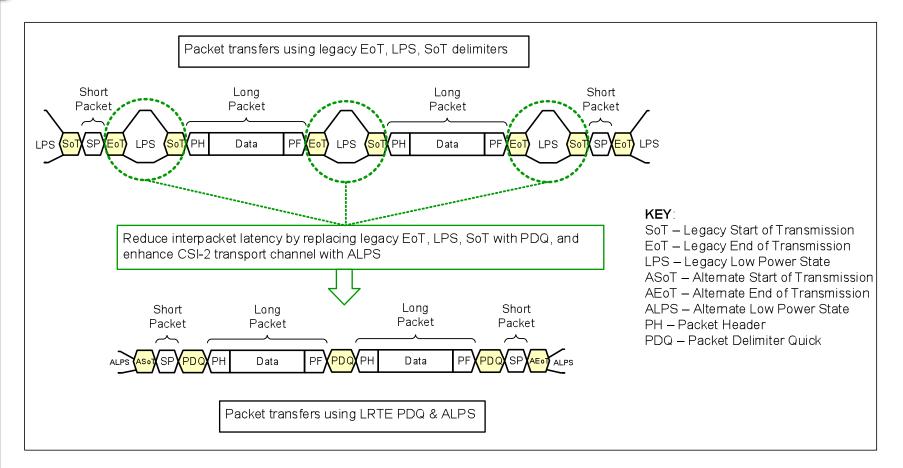

## **CSI-2 Latency Reduction Transport Efficiency**

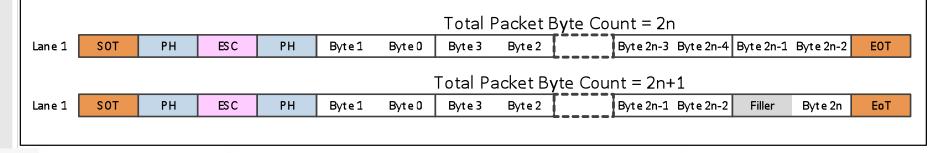

- Reduce latency and improve efficiency (preserving PHY based delimiters / B2B)

- Provides longer reach over C/D-PHYs without need for redrivers or retimers

- Alleviates electrical overstress current leakages impediments

Page 24

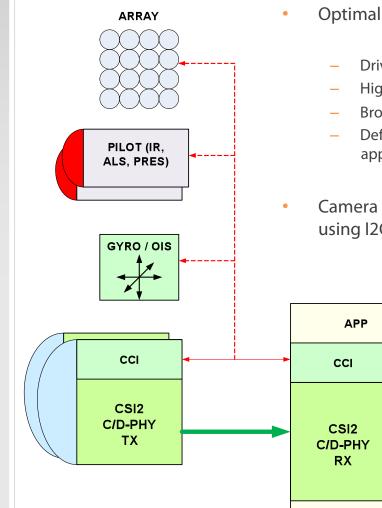

# **CSI-2** Sensor Fusion using CCI

mipi alliance

# CSI-2 CCI and AON Advancements 1/2

- Optimal pathway for multiple forward-looking advancements in imaging

- Drivers: Health, Convenience, Security, Lifestyle, Efficiency

- High-perf pixel conduit needs met with C/D-PHY advancements

- Broad definitions and fuzzy range: (i.e. Wearable: Near Body, On Body, In Body)

- Define imaging requirements for CCI, emerging AOI, array, and non-symmetrical applications

- Camera Controller Interface (CCI) and AON advancement considerations using I2C / I3C (SDR DDR, TSL, TSP)

- Point-to-Point and Multi-Drop configurations

## CSI-2 CCI and AON Advancements 2/2

## CSI-2 over C-PHY Virtual Channel Extension

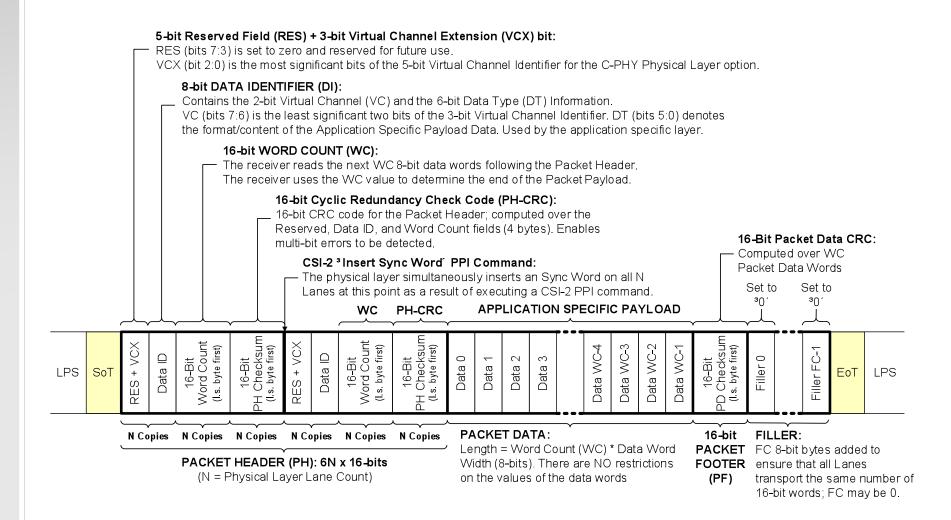

## **CSI-2** over D-PHY Virtual Channel Extension

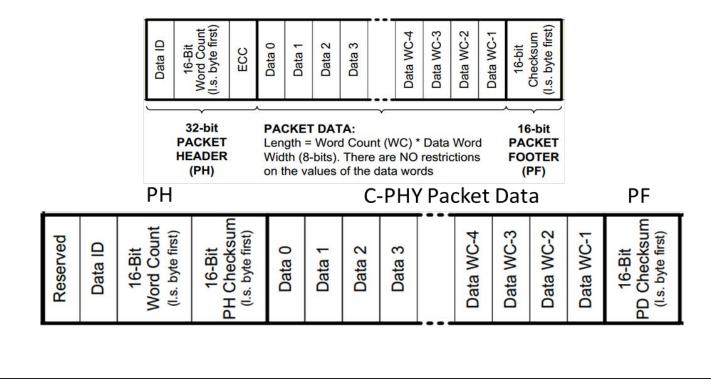

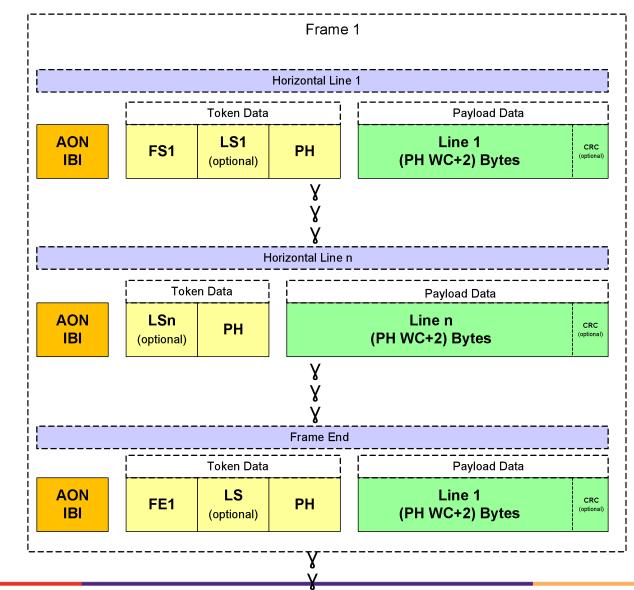

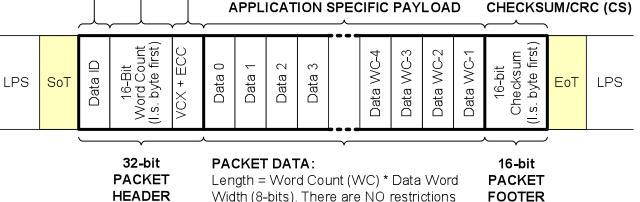

# 8-bit DATA IDENTIFIER (DI): Contains the 2-bit Virtual Channel (VC) and the 6-bit Data Type (DT) Information. VC (bits 7:6) is the least significant two bits of the 3-bit Virtual Channel Identifier. DT (bits 5:0) denotes the format/content of the Application Specific Payload Data. Used by the application specific layer. 16-bit WORD COUNT (WC):

The receiver reads the next WC data words independent of their values. The receiver is NOT looking for any embedded sync sequences within the payload data. The receiver uses the WC value to determine the end of the Packet Payload.

#### 6-bit Error Correction Code (ECC) + 2 Virtual Channel Extension (VCX) bits

ECC (bits 5:0) enables 1-bit errors within the packet header to be corrected and 2-bit errors to be detected. VCX (bits 7:6) are the most significant bit of the 4-bit Virtual Channel Identifier for the D-PHY physical layer option.

on the values of the data words.

(PH)

(PF)

## SI-2 DPCM & HDR Advancements

- DPCM 12-10-12

- SNR & IQ Benefits over varying degrees of noise, edges, MTF

- Superior to straight RAW-10 capture or existing DPCM 12-8-12

#### **SI-2 HDR Advancements HDR-16** P1[15:8] (A) P1[7:0] (A) P2[15:8](B) P2[7:0](B) Data A9 A10 A11 A12 A13 A14 A15 B9 B10 B11 B12 B13 B14 B15 B3 A8 A0 A2 A3 A4 A5 A6 A7 B8 BO B1 B2 В4 B5 A1 8-bits 8-bits 8-bits 8-bits Byte Values Transmitted LS Bit First Byte n+1 Byte n+2 Byte n+3 Byte n b0 b1 b2 b3 b4 b5 b6 b7 HDR-20 P1[19:12] (A) P1[9:2] (A) P2[19:12](B) P2[9:2] (B) A12 A13 A14 A15 A16 A17 A18 A1 A2 A3 A4 A5 A6 A7 A8 B12 B13 B14 B15 B16 B17 B18 B19 Data B3 B4 B5 B6 B7 B8 B2 BS **P1 P1 P2 P2** [11:10] [1:0] [11:10] [1:0] P3[19:12] (C) P4[19:12](D) P3[9:2] (C) 10 A11 A0 A1 B10 B11 B0 B1 C12 C13 C14 C15 C16 C17 C18 C19 C2 C3 C4 C5 C6 C7 C8 C9 D12 D13 D14 D15 D16 D17 D18 D16 8-bits 8-bits - 8-bits 8-bits Byte Values Transmitted LS Bit First Byte n+2 Byte n Byte n+1 Byte n+3 b0 b1 b2 b3 b4 b5 b6 b7 b0 b1 b2 b3 b4 b5 b6 b1

mipi<sup>alliance</sup>

B6 В7

mipralliance

mipralliance

Copyright © 2013 MIPI Alliance. All rights reserved.

## MIPI C/D/M PHYs

#### **PHY Characteristics**

| Characteristic                          | M-PHY v3.1                                                                                                  | D-PHY v1.2                                                                                    | C-PHY v1.0                                                                                    |

|-----------------------------------------|-------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|

| Primary use case                        | Performance driven,<br>bidirectional packet/<br>network oriented<br>interface                               | Efficient unidirectional<br>streaming interface,<br>with low speed in-band<br>reverse channel | Efficient unidirectional<br>streaming interface,<br>with low speed in-band<br>reverse channel |

| HS clocking method                      | Embedded Clock                                                                                              | DDR Source-Sync Clock                                                                         | Embedded Clock                                                                                |

| Channel compensation                    | Equalization                                                                                                | Data skew control<br>relative to clock                                                        | Encoding to reduce data toggle rate                                                           |

| Minimum configuration<br>and pins       | 1 lane per direction,<br>dual-simplex, 2 pins each<br>(4 total)                                             | 1 lane plus clock,<br>simplex, 4 pins                                                         | 1 lane (trio), simplex, 3<br>pins                                                             |

| Maximum transmitter<br>swing amplitude  | SA: 250mV (peak)<br>LA: 500mV (peak)                                                                        | LP: 1300mV (peak)<br>HS: 360mV (peak)                                                         | LP: 1300mV (peak)<br>HS: 425mV (peak)                                                         |

| Data rate per lane (HS)                 | HS-G1: 1.25, 1.45 Gb/s<br>HS-G2: 2.5, 2.9 Gb/s<br>HS-G3: 5.0, 5.8 Gb/s<br>(Line rates are 8b10b<br>encoded) | 80 Mbps to ~2.5 Gbps<br>(aggregate)                                                           | 80 Msym/s to 2.5 Gsym/s<br>times 2.28 bits/sym,<br>or max 5.7 Gbps<br>(aggregate)             |

| Data rate per lane (LS)                 | 10kbps – 600 Mbps                                                                                           | < 10 Mbps                                                                                     | < 10 Mbps                                                                                     |

| Bandwidth per Port<br>(3 or 4 lanes)    | ~ 4.0 – 18.6 Gb/s<br>(aggregate BW)                                                                         | Max ~10 Gbps per 4-lane<br>port (aggregate)                                                   | Max ~ 17.1 Gbps per<br>3-lane port (aggregate)                                                |

| Typical pins per Port<br>(3 or 4 lanes) | 10 (4 lanes TX, 1 lane RX)                                                                                  | 10 (4 lanes, 1 lane clock)                                                                    | 9 (3 lanes)                                                                                   |

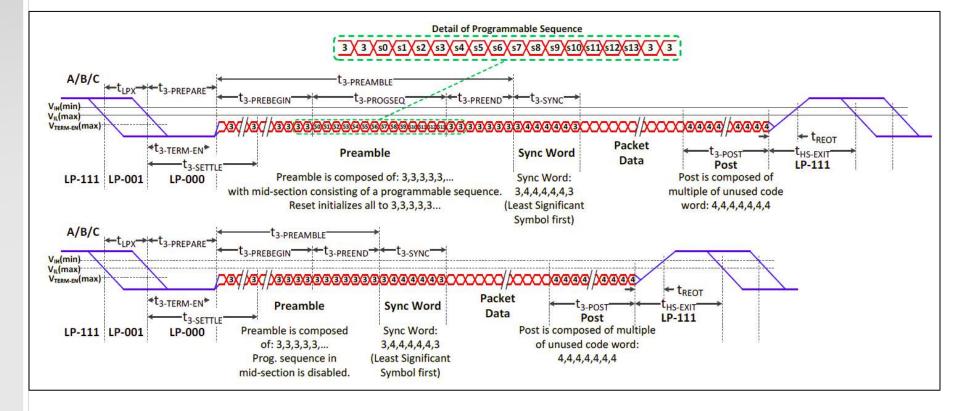

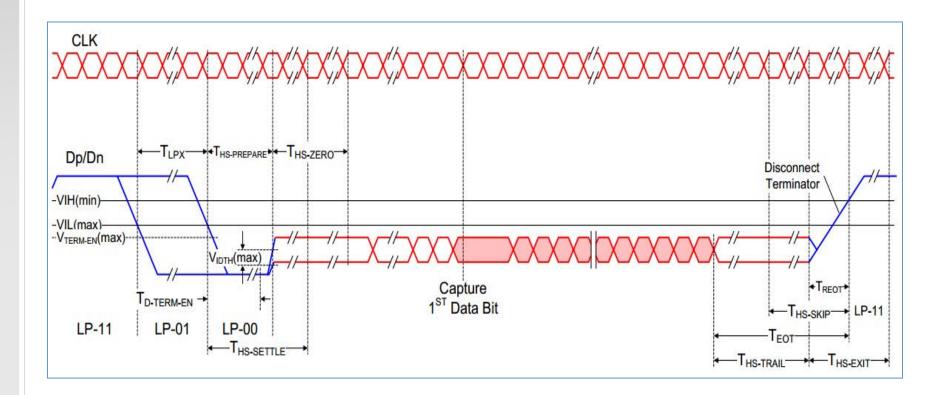

# CSI-2 over D-PHY signaling

# CSI-2 over C-PHY (N-Phase) signaling