### Universal Solution to Sideband Proliferation Using MIPI Virtual GPIO Interface

Lalan Mishra, Qualcomm Satwant Singh, Lattice Semiconductor John Oakley, Intel Date: 05/10/16

The material contained herein is not a license, either expressly or impliedly, to any IPR owned or controlled by any of the authors or developers of this material or MIPI<sup>®</sup>. The material contained herein is provided on an "AS IS" basis and to the maximum extent permitted by applicable law, this material is provided AS IS AND WITH ALL FAULTS, and the authors and developers of this material and MIPI hereby disclaim all other warranties and conditions, either express, implied or statutory, including, but not limited to, any (if any) implied warranties, duties or conditions of merchantability, of fitness for a particular purpose, of accuracy or completeness of responses, of results, of workmanlike effort, of lack of viruses, and of lack of negligence. ALSO, THERE IS NO WARRANTY OR CONDITION OF TITLE, QUIET ENJOYMENT, QUIET POSSESSION, CORRESPONDENCE TO DESCRIPTION OR NON-INFRINGEMENT WITH REGARD TO THIS MATERIAL.

All materials contained herein are protected by copyright laws, and may not be reproduced, republished, distributed, transmitted, displayed, broadcast or otherwise exploited in any manner without the express prior written permission of MIPI Alliance. MIPI, MIPI Alliance and the dotted rainbow arch and all related trademarks, tradenames, and other intellectual property are the exclusive property of MIPI Alliance and cannot be used without its express prior written permission.

IN NO EVENT WILL ANY AUTHOR OR DEVELOPER OF THIS MATERIAL OR MIPI BE LIABLE TO ANY OTHER PARTY FOR THE COST OF PROCURING SUBSTITUTE GOODS OR SERVICES, LOST PROFITS, LOSS OF USE, LOSS OF DATA, OR ANY INCIDENTAL, CONSEQUENTIAL, DIRECT, INDIRECT, OR SPECIAL DAMAGES WHETHER UNDER CONTRACT, TORT, WARRANTY, OR OTHERWISE, ARISING IN ANY WAY OUT OF THIS OR ANY OTHER AGREEMENT RELATING TO THIS MATERIAL, WHETHER OR NOT SUCH PARTY HAD ADVANCE NOTICE OF THE POSSIBILITY OF SUCH DAMAGES.

### 省 Agenda

| # | Торісѕ                                                              | Speaker(s)                                                                  | Time (Minutes) |

|---|---------------------------------------------------------------------|-----------------------------------------------------------------------------|----------------|

| 1 | Opening and Speaker Self-Introduction                               | Peter Lefkin<br>Lalan Mishra<br>Satwant Singh<br>John Oakley<br>Laura Nixon | 05             |

| 2 | MIPI : A Brief Overview                                             | Peter Lefkin                                                                | 05             |

| 2 | The Issue of Sideband Proliferation and The Need to address it      | Satwant Singh                                                               | 05             |

| 3 | Virtual GPIO Interface (VGI): Concept and<br>Architectural Overview | Lalan Mishra                                                                | 20             |

| 4 | VGI in relation to other familiar Interfaces                        | John Oakley                                                                 | 07             |

| 5 | MIPI VGI Timeline                                                   | Laura Nixon                                                                 | 03             |

| 6 | Summary                                                             | Lalan Mishra                                                                | 05             |

| 7 | Q&A                                                                 | All                                                                         | 10             |

### Brief overview from Peter Lefkin

#### Managing Director, MIPI Alliance

Copyright © 2016 MIPI Alliance. All rights reserved.

5/10/16 Page 3

### About MIPI Alliance

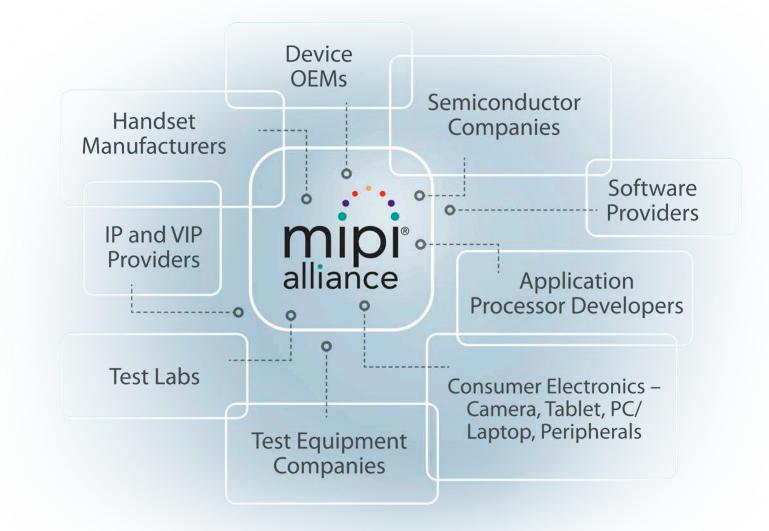

We are a global, collaborative organization comprised of over 250 member companies spanning the mobile and mobile-influenced ecosystems.

MIPI Alliance is leading innovation in mobile interface technology.

### MIPI Alliance Member Ecosystem

5/10/16 Page 5

#### mipralliance

### **Partners**

MIPI Alliance is proud to be a part of the mobile device industry. While our interest is focused on interfaces within mobile device design, we recognize and appreciate other organizations which also support this industry.

JEDEC MEMS Industry Group PCI-SIG UFSA USB Implementers Forum, Inc. VESA

5/10/16 Page 7

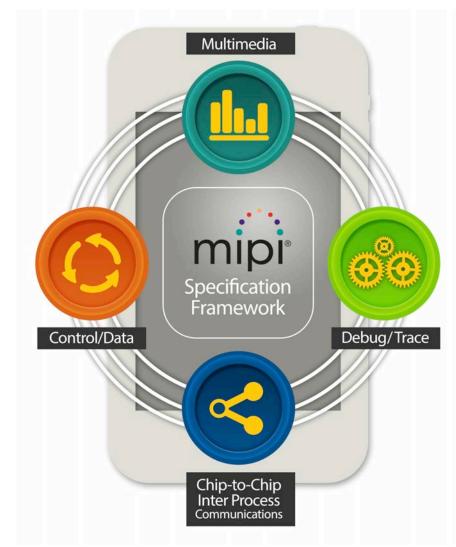

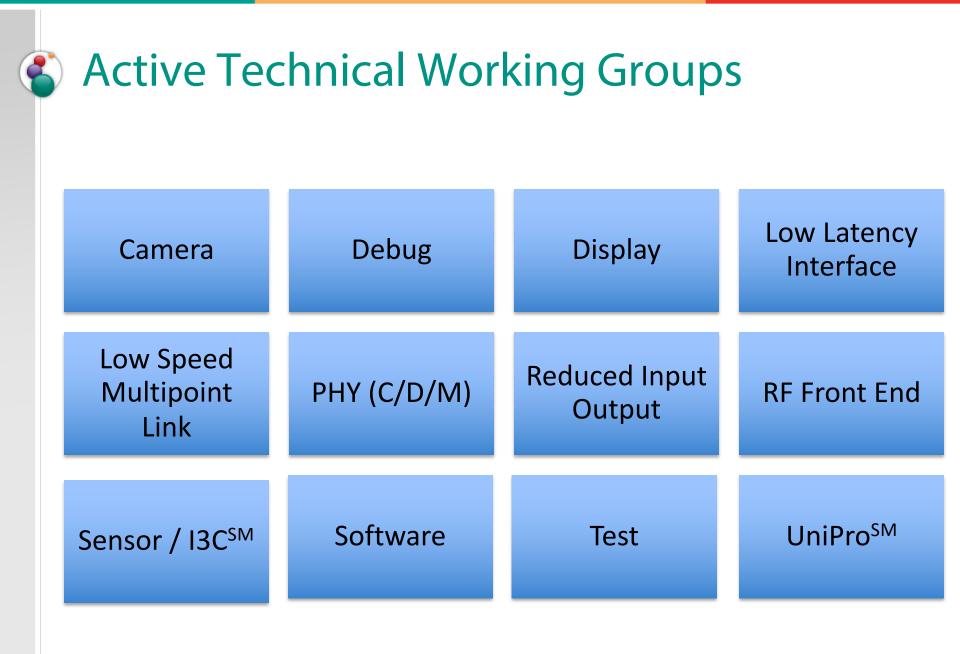

**MIPI** Alliance continues to evolve its Roadmap to meet the needs of the mobile and mobileinfluenced industry with new and revised specifications.

Roadmap

mipiralliance

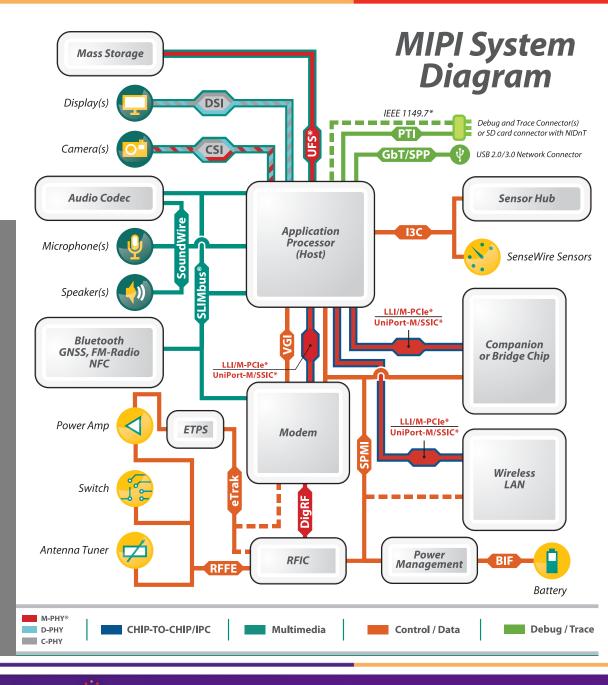

### **The Issue of Sideband Proliferation**

### Mobile Connectivity Expansion Trends

#### Cellular

#### WiFi

■ 802.11a/b/g/n/ac → 802.11ad/WiGig

#### Video

□ VGA/SD/HD → 4K

#### Docking

Charging/audio/video →

Productivity, Games and External

Storage

#### 5/10/16 Page 10

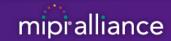

### The Problem of Sideband Proliferation

#### mipi<sup>alliance</sup>

### Virtual GPIO Interface: Concept and Architectural Overview

### VGI :: The Concept

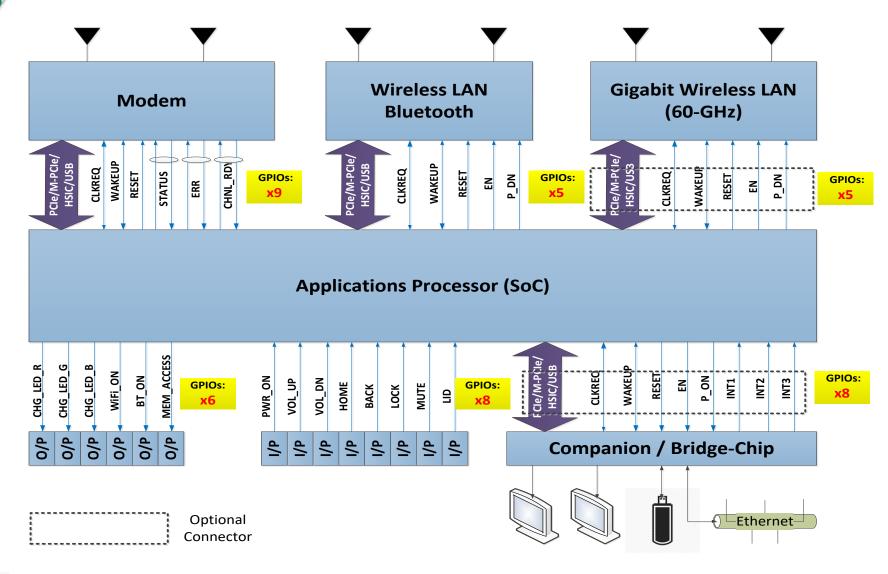

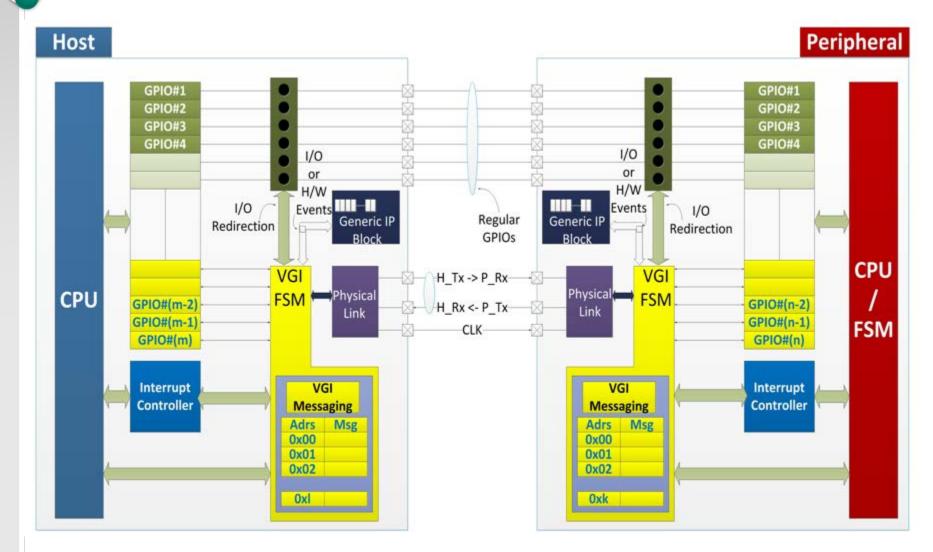

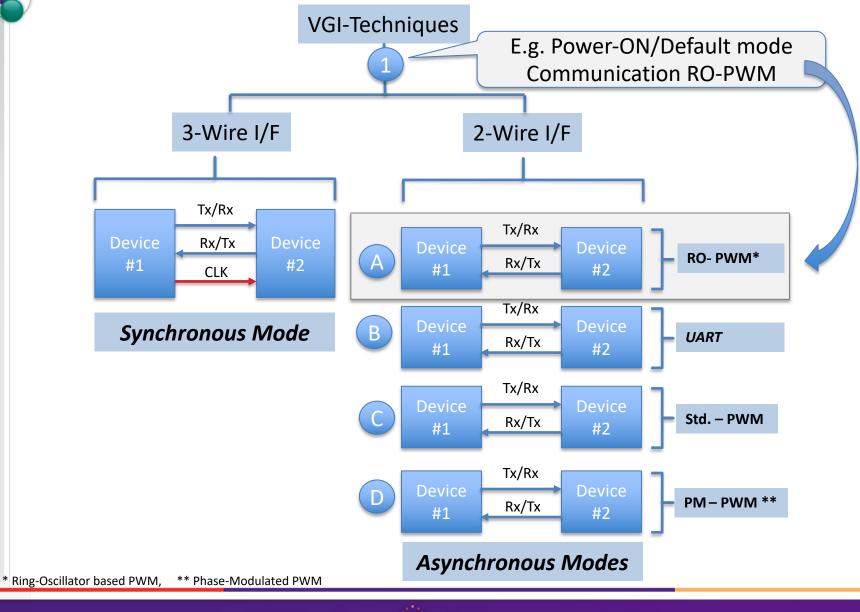

- VGI consolidates N-sideband GPIOs and sub-100 MHz serial messaging over **2** or **3** wire interface in a Point-to-Point configuration

- 2-wire VGI : Asynchronous, Full-Duplex

- **3-wire VGI** : Synchronous, Full-Duplex

- VGI Rev-1 Max Speed: 38.4MHz

**Consolidates Low Speed Messaging Interface and**  $\checkmark$ and Sideband GPIOs (N-pins to 2/3-pins reduction)

(Opt.)

#### Limitation of Conventional Techniques SoC **Low Power** Clock Mode Generator System Manager C<sub>2</sub>C Comm. IP SoC Sub-System SoC Internal Bus IPC side-band Bus Block **Core Processor**

- ✓ HLOS processing latency varies widely

- ✓ Deep-sleep to active-state typical latency : Typically → 30 to 100-mS

- Timing uncertainty not suitable for the key IPC side-band signaling

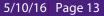

### Searchitectural Block-Diagram

5/10/16 Page 16

#### mipralliance

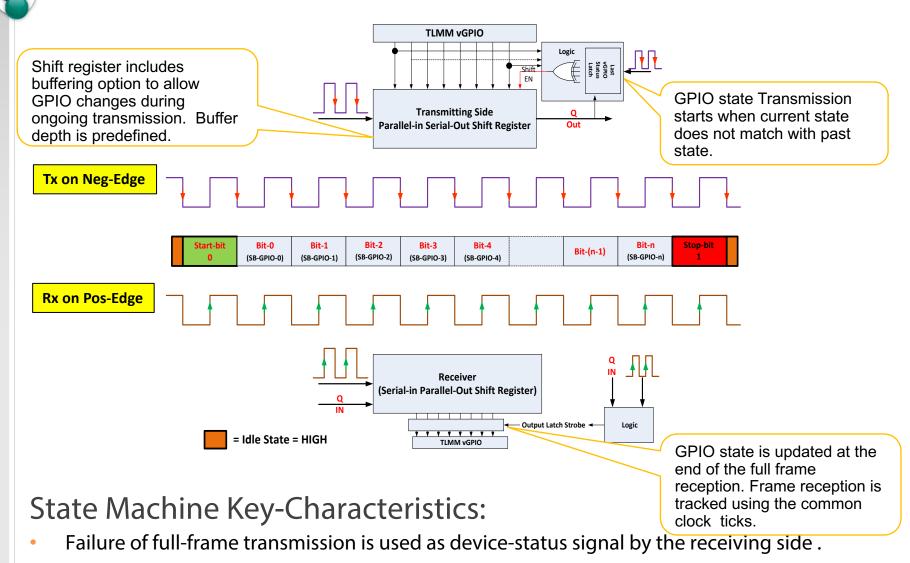

### VGI Physical Interface Characteristics

1

2

Initial and Power State Transition mode communication over 2-wire

#### Synchronous VGI

- Common clock (Up to 38.4 MHz in VGI Rev-1)

- Sleep clock based operation supported in Low Power Modes

### **VGI Techniques At-a-Glance**

2

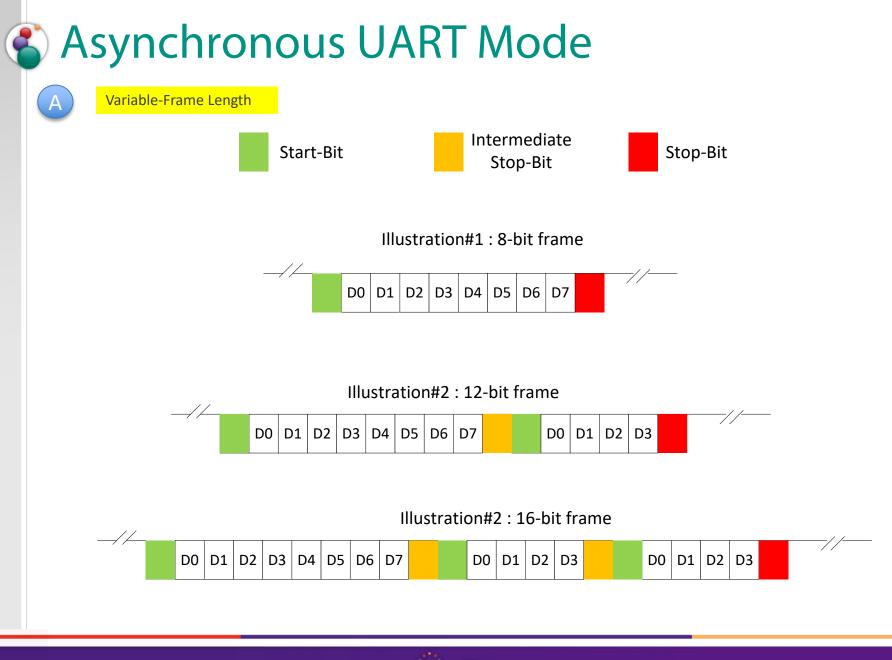

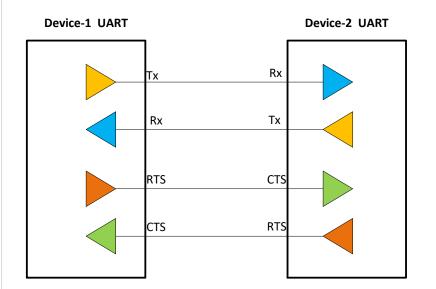

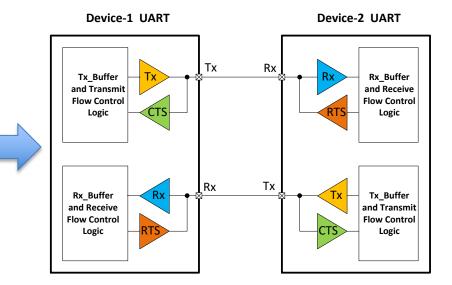

### S Asynchronous UART Mode

H/W Flow Control over Tx/Rx eliminates RTS/CTS physical pins

#### mipralliance

### Asynchronous VGI: Phase-Modulated

#### Highlights:

- All Digital Solution

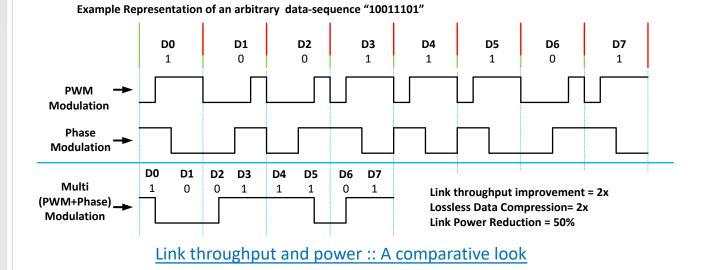

- 2x Throughput

- Time-domain data compression

- Link power Reduction by 50%

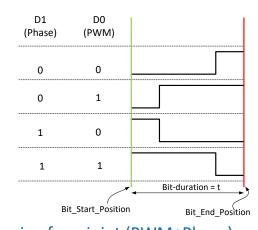

#### Symbol to signal mapping for a joint (PWM+Phase) modulation scheme

5/10/16 Page 21

P\//M

#### mipralliance

### Synchronous 3-Wire VGI

#### 5/10/16 Page 22

#### mipralliance

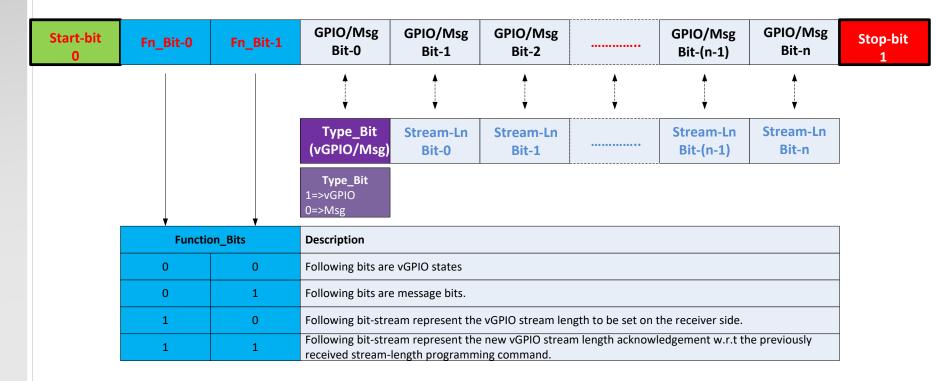

### SVGI Protocol – 1 of 3

**NOTE**: The mechanism has a fixed overhead of two-bits over the base-line vGPIO implementation.

- Addresses P2P VGI link requirements only

- Only 2-bitsrequired as function bits. A 3<sup>rd</sup> function bit used during link length programming.

### SVGI Protocol – 2 of 3

| Start-bit<br>0 | Fn_Bit-0 | Fn_Bit-1 | Fn_Bit-2                                                                                                                                    | GPIO/Msg<br>Bit-0       | GPIO/Msg<br>Bit-1  |                | GPIO/Msg<br>Bit-(n-1)  | GPIO/Msg<br>Bit-n  | Stop-bit<br>1     |

|----------------|----------|----------|---------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|--------------------|----------------|------------------------|--------------------|-------------------|

|                |          |          |                                                                                                                                             | ţ                       | <b>↓</b>           |                | ţ                      | ţ                  |                   |

|                |          |          | Type_Bit<br>(vGPIO/Msg)                                                                                                                     | Stream-Ln<br>Bit-0      | Stream-Ln<br>Bit-1 |                | Stream-Ln<br>Bit-(n-1) | Stream-Ln<br>Bit-n | Fn_Bit_2          |

|                |          |          | <b>Type_Bit</b><br>1=>vGPIO<br>0=>Msg                                                                                                       |                         |                    |                |                        |                    | > In Prog<br>Mode |

|                |          |          | Comm<br>Mode                                                                                                                                | 0 => P2P<br>1=> P2MP; t | he following in    | nmediate 8-bit | s are destinatio       | on address         |                   |

|                | Functio  | on_Bits  | Description                                                                                                                                 |                         |                    |                |                        |                    |                   |

|                | 0        | 0        | Following bits are vGPIO states                                                                                                             |                         |                    |                |                        |                    |                   |

|                | 0        | 1        | Following bits are message bits.                                                                                                            |                         |                    |                |                        |                    |                   |

|                | 1        | 0        | Following bit-stream represent the vGPIO stream length to be set on the receiver side.                                                      |                         |                    |                |                        |                    |                   |

|                | 1        | 1        | Following bit-stream represent the new vGPIO stream length acknowledgement w.r.t the previously received stream-length programming command. |                         |                    |                |                        |                    |                   |

**NOTE**: The mechanism has a fixed overhead of three-bits over the base-line vGPIO implementation.

- Addresses P2P and P2MP links.

- No provision for error-detection and correction capability.

#### 5/10/16 Page 24

#### mipiralliance

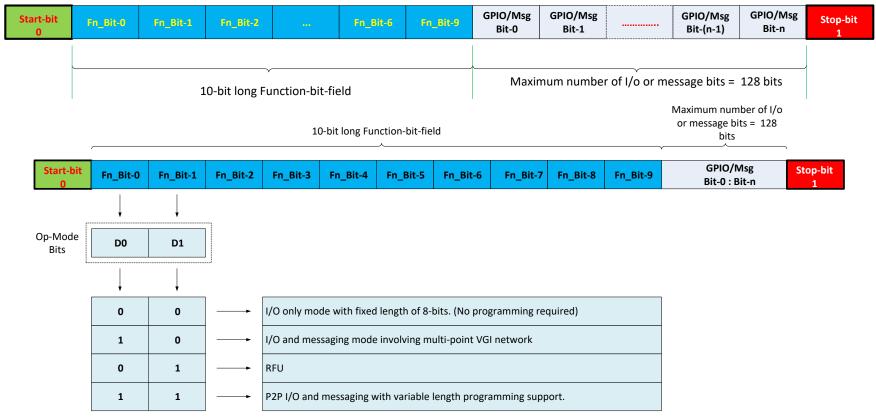

### SVGI Protocol – 3 of 3

- Uses 10-bits (maximum) in the Function-bit-field

- First two function bits are used for operation mode setting

- The remaining 8-bits (Mode "10") are Extended Hamming (8,4) coded 8-bit code words defining unique functions

- Provides option for easy expansion to add new functions

#### mipralliance

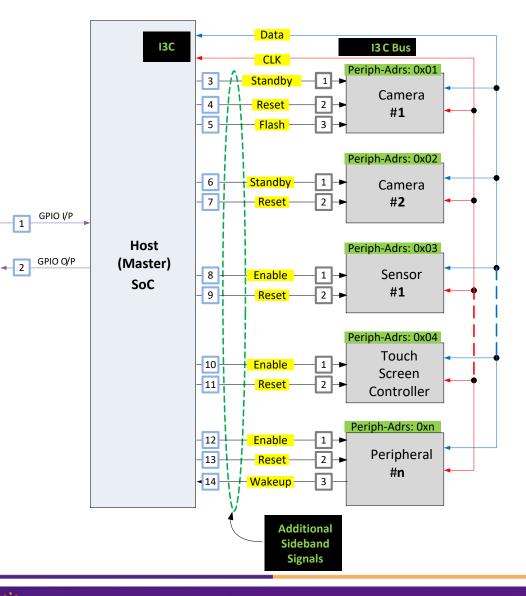

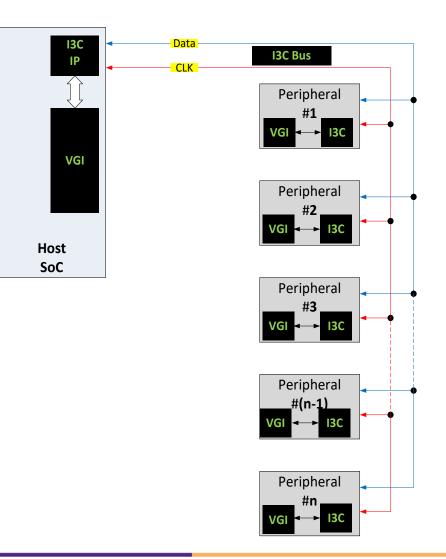

### VGI FSM Integration with I3C (I3C\_VGI)

- VGI FSM could be integrated with a serial interface of choice, such as I3C

- MIPI I3C supports VGI integration through command code support

- Helps reduce Hardware event pins at system level

### VGI FSM Integration with I3C (I3C\_VGI)

- HW Event sideband signals are eliminated

- VGI-FSM (Finite State Machine) performs I3C message encoding/decoding for HW events and thus frees up the associated CPU on the host-SoC for these tasks.

- Impact is reduced Latency and Power consumption.

#### mipi<sup>alliance</sup>

### **VGIO in Relation to Other Interfaces**

### Some and the second sec

Comparison of Various Low Speed Interfaces

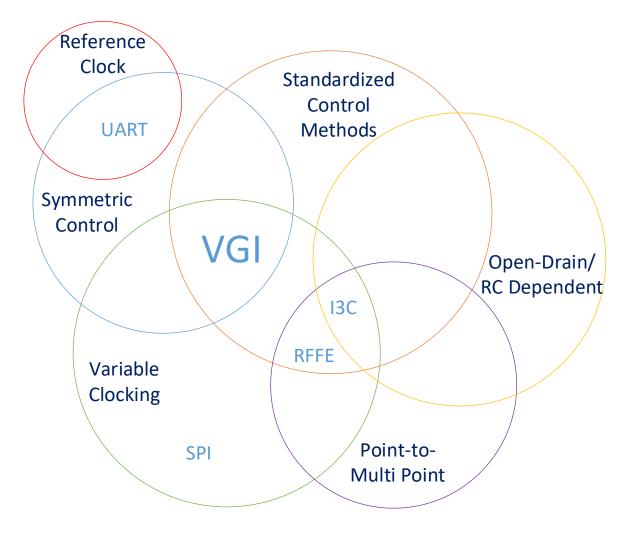

## Comparing VGI with Low speed interfaces

- SPI

- Master-Slave approach

- Custom implementations, no common methods

- I3C

- Master-Multi Slave, Open-Drain approach

- In-band interrupts

- RFFE

- Master-Multi Slave approach

- UART

- Custom implementations, requires reference clocks

- VGI

- Symmetric control approach (No Master No Slave)

- Initialization from either side

### Source of the second se

### • UART

Requires Reference Clock with Agreed rates

### • SPI, I3C, RFFE

Clock is forwarded from Master to Slave

### • VGI

- Using RO-PWM PHY option, the clocking is forwarded with data

- Only Transmitter requires clock to create telegrams

- Receiving side captures telegrams without internal clock

- Useful for devices which power down

- Useful for very simple write-only devices (LED bank)

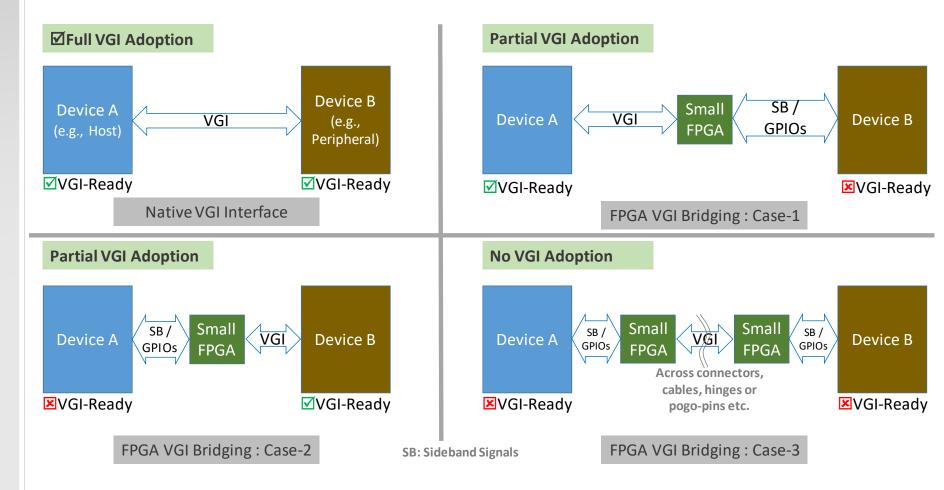

### Phased VGI Adoption – Leveraging Smaller FPGAs

Sideband GPIOs add to SoC and PCB level cost and complexity

MIPI VGI Architecture consolidates sideband GPIOs and Low-Speed serial interface in P2P configuration to reduce I/O pins

Both 2 and 3-wire interface options are available

Common start-up mode ensures interoperability

The VGI FSM can be combined with any other interface bus of choice, e.g. I3C\_VGI

The VGI specification is to be released later this year

#### mipi<sup>alliance</sup>

## Questions?

# Thank You! alliance